# THE UNIVERSITY OF WARWICK

#### AUTHOR: Catarina Beatriz Antunes Casteleiro DEGREE: Ph.D.

#### **TITLE: Electrical and Physical Characterization of Ge Devices**

DATE OF DEPOSIT: .....

I agree that this thesis shall be available in accordance with the regulations governing the University of Warwick theses.

I agree that the summary of this thesis may be submitted for publication.

I **agree** that the thesis may be photocopied (single copies for study purposes only).

Theses with no restriction on photocopying will also be made available to the British Library for microfilming. The British Library may supply copies to individuals or libraries. subject to a statement from them that the copy is supplied for non-publishing purposes. All copies supplied by the British Library will carry the following statement:

> "Attention is drawn to the fact that the copyright of this thesis rests with its author. This copy of the thesis has been supplied on the condition that anyone who consults it is understood to recognise that its copyright rests with its author and that no quotation from the thesis and no information derived from it may be published without the author's written consent."

AUTHOR'S SIGNATURE: .....

#### USER'S DECLARATION

- 1. I undertake not to quote or make use of any information from this thesis without making acknowledgement to the author.

- 2. I further undertake to allow no-one else to use this thesis while it is in my care.

| DATE | SIGNATURE | ADDRESS |

|------|-----------|---------|

|      |           |         |

|      |           |         |

|      |           |         |

|      |           |         |

|      |           |         |

# Electrical and Physical Characterization of Ge Devices

by

#### Catarina Beatriz Antunes Casteleiro

Thesis

Submitted to The University of Warwick

for the degree of

Doctor of Philosophy

**Physics Department**

March 2014

# Contents

| List of | Tables                                  | v     |

|---------|-----------------------------------------|-------|

| List of | Figures                                 | vi    |

| Ackno   | wledgments                              | xv    |

| Declar  | ations                                  | xvii  |

| Abstra  | act                                     | xviii |

| Public  | ations                                  | xix   |

| 0.1     | Publications                            | xix   |

| 0.2     | Participations/attendance in Conference | XX    |

| Chapt   | er 1 Introduction                       | 1     |

| 1.1     | Motivation                              | 1     |

| 1.2     | Basic properties of Si and Ge           | 4     |

| 1.3     | Strained layers                         | 7     |

| 1.4     | Ge surface passivation                  | 9     |

| 1.5     | Thesis outline                          | 11    |

| Chapt   | er 2 Theoretical Background             | 12    |

| 2.1     | Metal-Oxide-Semiconductor capacitors    | 12    |

|         | 2.1.1 MOS CV characteristics            | 17    |

| 2.2    | Metal  | -Oxide-Semiconductor Field-Effect-Transistor (MOSFET). | 18 |

|--------|--------|--------------------------------------------------------|----|

| 2.3    | Carrie | er Mobility and Scattering                             | 22 |

|        | 2.3.1  | Scattering mechanisms                                  | 23 |

| 2.4    | Magne  | eto Transport theory                                   | 26 |

|        | 2.4.1  | The Hall effect                                        | 26 |

|        | 2.4.2  | Shubnikov-de-Haas effect                               | 29 |

| Chapte | er 3 H | Experimental Techniques                                | 31 |

| 3.1    | Sampl  | le growth and preparation                              | 31 |

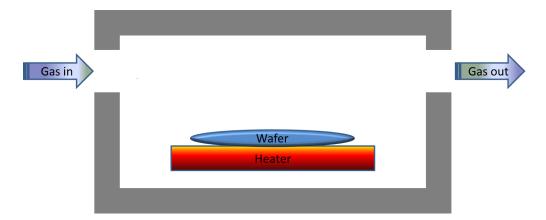

|        | 3.1.1  | Chemical Vapour Deposition.                            | 32 |

|        | 3.1.2  | Evaporation                                            | 33 |

|        | 3.1.3  | Lithography                                            | 34 |

|        | 3.1.4  | Atomic Layer Deposition.                               | 36 |

| 3.2    | Electr | ical and structural characterization                   | 37 |

|        | 3.2.1  | Current-Voltage measurements                           | 40 |

|        | 3.2.2  | Capacitance-Voltage measurement                        | 41 |

|        | 3.2.3  | Resistivity and Hall measurements                      | 42 |

|        | 3.2.4  | X-Ray Photoemission Spectroscopy                       | 45 |

| 3.3    | Data   | analyses techniques                                    | 46 |

|        | 3.3.1  | Threshold Voltage                                      | 46 |

|        | 3.3.2  | Subthreshold Slope                                     | 48 |

|        | 3.3.3  | Parasitic Resistance and Resistivity                   | 49 |

|        | 3.3.4  | Oxide Capacitance and Equivalent Oxide                 |    |

|        |        | Thickness                                              | 53 |

|        | 3.3.5  | Flatband Voltage                                       | 54 |

|        | 3.3.6  | Effective mobility and effective field                 | 55 |

|        | 3.3.7         | Hall mobility and effective mass.                                    | 56  |

|--------|---------------|----------------------------------------------------------------------|-----|

| Chapte | er 4 (        | Germanium pMOSFETs                                                   | 60  |

| 4.1    | Device        | e description                                                        | 62  |

| 4.2    | Device        | e characteristics                                                    | 64  |

|        | 4.2.1         | Effect of passivation                                                | 69  |

|        | 4.2.2         | Effect of sGe channel thickness                                      | 75  |

|        | 4.2.3         | Effect of doping.                                                    | 79  |

| 4.3    | Series        | Resistance                                                           | 80  |

| 4.4    | Concl         | usion                                                                | 84  |

| Chapte | er 5 H        | High mobility strained Ge QW heterostructures.                       | 86  |

| 5.1    | 2DHG          | grown by CVD and MBE.                                                | 87  |

| 5.2    | Hetero        | ostructures grown by CVD                                             | 94  |

|        | 5.2.1         | Structural analysis.                                                 | 95  |

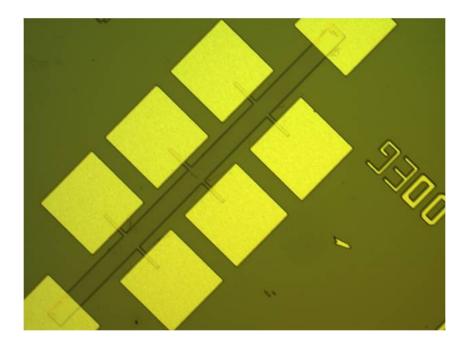

|        | 5.2.2         | Hall Bar fabrication.                                                | 96  |

|        | 5.2.3         | Mobility measurements                                                | 98  |

|        | 5.2.4         | Magnetotransport measurements                                        | 99  |

| 5.3    | Conclu        | usion                                                                | 107 |

| Chapte | er6 (         | Germanium Oxide                                                      | 109 |

| 6.1    | Introd        | luction                                                              | 109 |

| 6.2    | Epitaz        | xial Ge layer growth                                                 | 112 |

| 6.3    | ${\rm GeO}_2$ | oxidation formation                                                  | 113 |

|        | 6.3.1         | $GeO_2$ Oxidation System $\ldots \ldots \ldots \ldots \ldots \ldots$ | 113 |

|        | 6.3.2         | Ge surface preparation and $GeO_2$ growth                            | 114 |

|        | 6.3.3         | Oxidation process                                                    | 115 |

| Bibliog              | Bibliography |                                                                                                |     |

|----------------------|--------------|------------------------------------------------------------------------------------------------|-----|

| Chapter 7 Conclusion |              |                                                                                                | 142 |

| 6.7                  | Summ         | ary                                                                                            | 140 |

| 6.6                  | Discus       | sion $\ldots$ | 139 |

|                      | 6.5.2        | Oxidation results                                                                              | 124 |

|                      | 6.5.1        | Preliminary studies.                                                                           | 119 |

| 6.5                  | Result       | s of the $\text{GeO}_x$ layers                                                                 | 119 |

|                      | 6.4.1        | XPS analysis                                                                                   | 116 |

| 6.4                  | Chara        | cterization of Oxide layers                                                                    | 116 |

# List of Tables

| 1.1 | Basic parameter of Semiconductors                                        | 5   |

|-----|--------------------------------------------------------------------------|-----|

| 1.2 | Dielectric constant of candidate gate dielectrics                        | 10  |

| 4.1 | Label of the different wafers, according to passivation type,            |     |

|     | thickness and doping                                                     | 65  |

| 6.1 | Selected electrical parameters for the capacitors in test batch.         | 121 |

| 6.2 | Matrix of oxidation times and oxidation temperatures used                | 124 |

| 6.3 | Selected electrical parameters for the $Al/GeO_2Ge$ capacitors           |     |

|     | from the third oxidation and a comparison of oxide thickness             |     |

|     | measured by CV and TEM. The $\mathbf{t}_{ox}$ values were calculated as- |     |

|     | suming a dielectric constant of 5                                        | 130 |

# List of Figures

| 1.1  | Energy band structure for Ge and Si                                         | 6  |

|------|-----------------------------------------------------------------------------|----|

| 1.2  | Variation of the band gap of $Si_{1-x}Ge_x$ , with Ge content               | 7  |

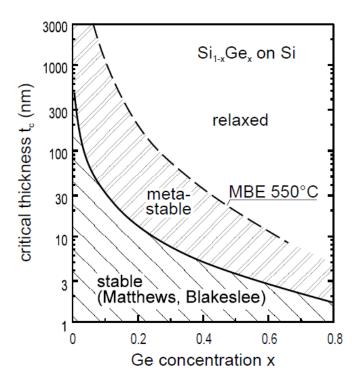

| 1.3  | Critical thickness as a function of Germanium composition                   | 8  |

| 2.1  | Schematic of a MOS capacitor.                                               | 12 |

| 2.2  | Energy band diagram for a MOS capacitor in flat<br>band. $\ .$              | 13 |

| 2.3  | Energy band diagram for a MOS capacitor in accumulation                     | 14 |

| 2.4  | Energy band diagram for a MOS capacitor in depletion                        | 15 |

| 2.5  | Energy band diagram for a MOS capacitor in inversion and                    |    |

|      | strong inversion                                                            | 16 |

| 2.6  | CV characteristics for a MOS capacitor for both high frequency              |    |

|      | and low frequency.                                                          | 18 |

| 2.7  | Schematic of a pMOSFET                                                      | 19 |

| 2.8  | Ideal output characteristics of a MOSFET                                    | 21 |

| 2.9  | Schematic showing the difference between the acoustic and op-               |    |

|      | tical phonons with the same wavelength. $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 24 |

| 2.10 | Schematic representation of phonon acoustic and optical modes.              | 25 |

| 3.1  | A simple illustration of the CVD process                                    | 33 |

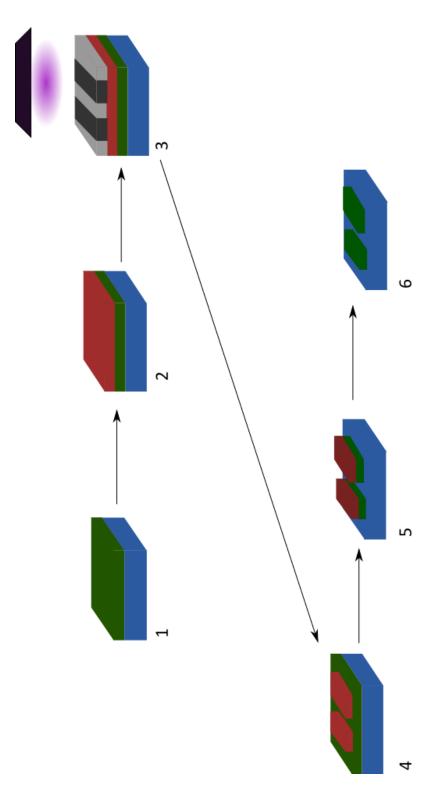

| 3.2  | Lithography process: 1) sample to process, 2) photoresit coat-              |    |

|      | ing, 3) exposing to UV light, 4) development, 5) etching and 6)             |    |

|      | photoresit removal.                                                         | 35 |

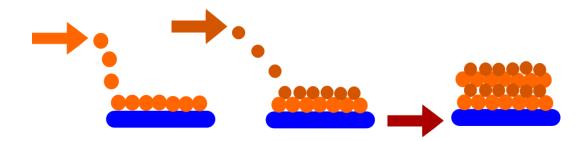

| 3.3  | A scheme of ALD process. The first precursor will be chemisorbed          |    |

|------|---------------------------------------------------------------------------|----|

|      | on the surface, as the surface saturates the second precursor is          |    |

|      | introduced reacting with the new surface until saturation. This           |    |

|      | process is repeated in order to get the desired thickness                 | 37 |

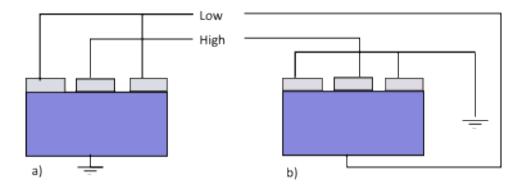

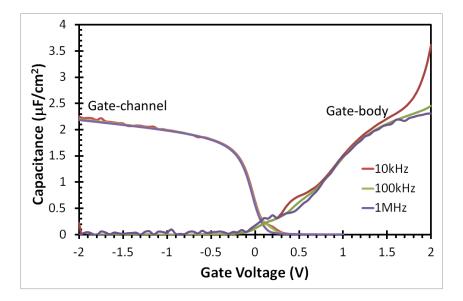

| 3.4  | Diagrams for measuring MOSFETs capacitances using the split-              |    |

|      | CV method exhibiting both branches: gate-channel (a) and                  |    |

|      | gate-body (b)                                                             | 42 |

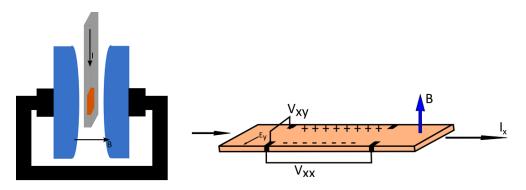

| 3.5  | Hall measurement set up $(\mathbf{left})$ and in plane view of the sample |    |

|      | $(\mathbf{right})$ for resistivity and Hall effect measurements           | 43 |

| 3.6  | Measurement configuration for measuring the Hall effect. On               |    |

|      | the left the Van der Pauw structure and on the right the Hall             |    |

|      | bar geometry.                                                             | 44 |

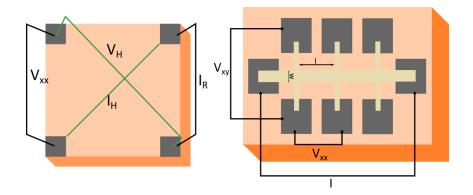

| 3.7  | Diagram of a XPS measurement.                                             | 45 |

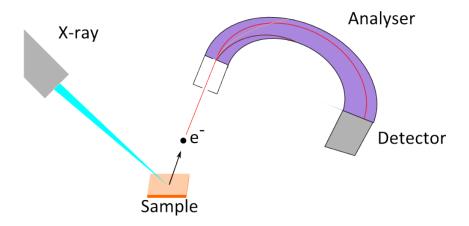

| 3.8  | Drain current (left) and transconductance (right) curves of a             |    |

|      | pMOSFET for the determination of threshold voltage. In both               |    |

|      | methods an extrapolation of the linear region to the voltage axis         |    |

|      | gives the threshold voltage                                               | 47 |

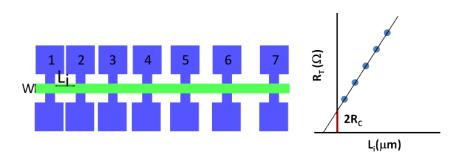

| 3.9  | Transmission line model test structure (TLM) and method to                |    |

|      | extract the contact resistance (right)                                    | 50 |

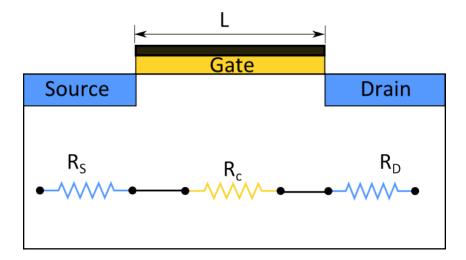

| 3.10 | Different contributions to the resistance in a MOSFET                     | 50 |

| 3.11 | Split-CV characteristics for a pMOSFET                                    | 55 |

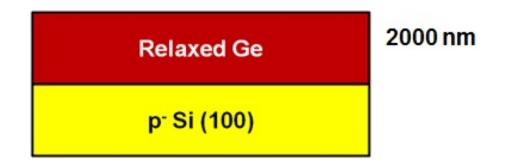

| 4.1  | Schematic diagram of the structures for relaxed germanium layers          | 62 |

|      |                                                                           |    |

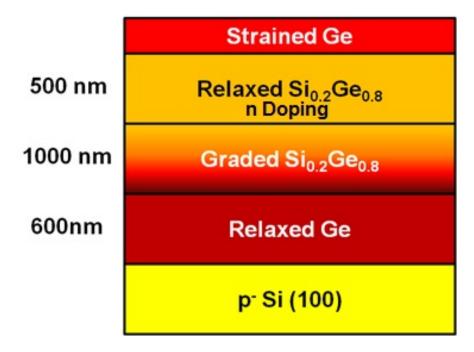

| 4.2  | Schematic diagram of the structures for strained germanium layers         | 62 |

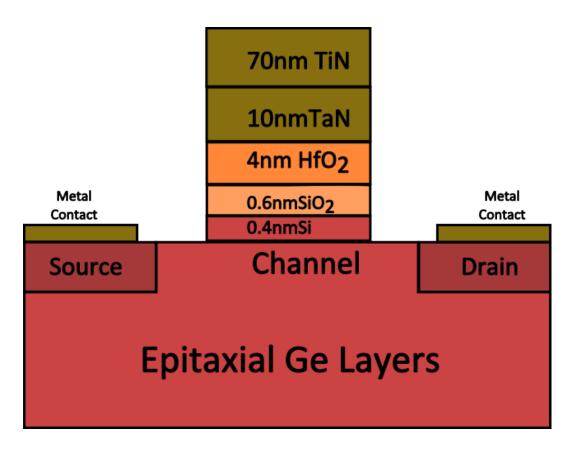

| 4.3  | Gate stack implemented by Atomic Laser Deposition at IMEC                 | 64 |

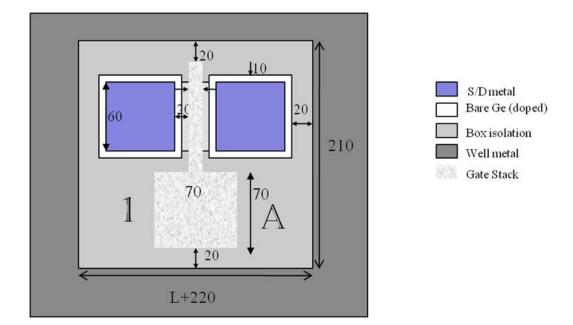

| 4.4  | Devices schematic (dimensions in $\mu$ m)                                 | 65 |

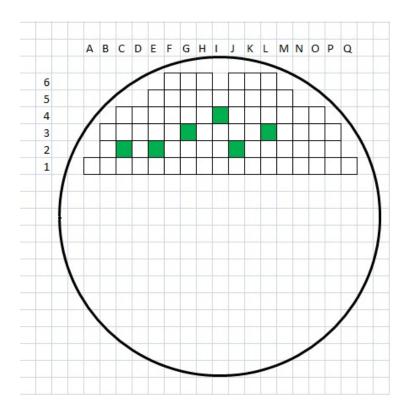

| 4.5  | Wafer map for uniformity study                                                         | 66 |

|------|----------------------------------------------------------------------------------------|----|

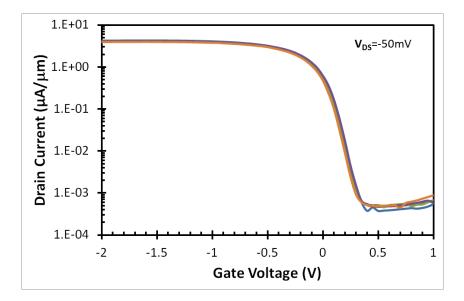

| 4.6  | Drain current curves for four devices, with the same dimensions                        |    |

|      | taken from different positions on the wafer, at room tempera-                          |    |

|      | ture. The wafer consisted of sGe layers, with a channel thickness                      |    |

|      | of 10 nm and a channel doping of $5 \times 10^{-17} \text{cm}^{-3}$                    | 67 |

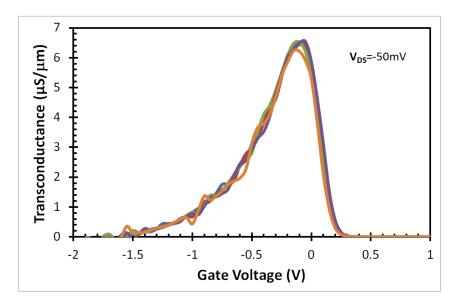

| 4.7  | Transconductance curves for the four devices shown in the pre-                         |    |

|      | vious figure. The wafer consisted of sGe layers, with a channel                        |    |

|      | thickness of 10 nm and a channel doping of $5\times 10^{-17} {\rm cm}^{-3}.$ .         | 67 |

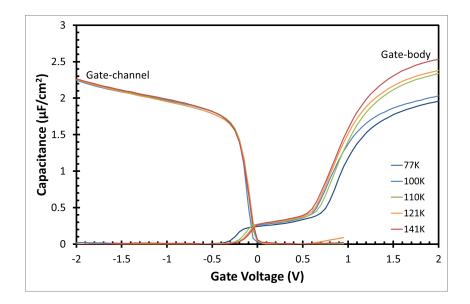

| 4.8  | Capacitance characteristics used to extract the oxide thickness                        |    |

|      | at different temperatures. The CV curves were obtained using                           |    |

|      | the split-CV techniques.                                                               | 68 |

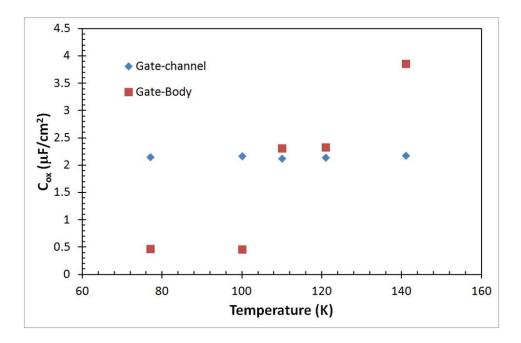

| 4.9  | Oxide capacitance extracted from the gate-channel and gate-                            |    |

|      | body branches of the split CV taken at different temperatures.                         | 69 |

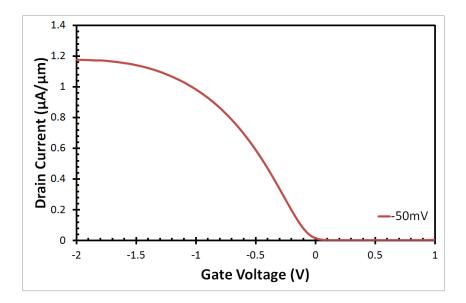

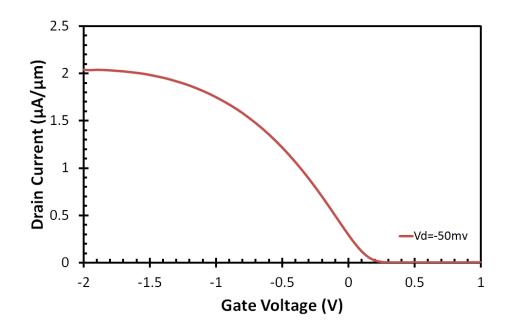

| 4.10 | Linear drain current taken for wafer with rGe layers and ${\rm Si_3H_8}$               |    |

|      | passivation scheme. The measurements were taken at room                                |    |

|      | temperature                                                                            | 70 |

| 4.11 | Capacitance characteristics in function of frequency for wafer                         |    |

|      | with rGe layers and $\mathrm{Si}_{3}\mathrm{H}_{8}$ passivation scheme. Both the gate- |    |

|      | channel and gate-body branch are shown. A small bump can                               |    |

|      | be seen in the depletion region as indicated by the arrow. The                         |    |

|      | measurements were taken at room temperature                                            | 70 |

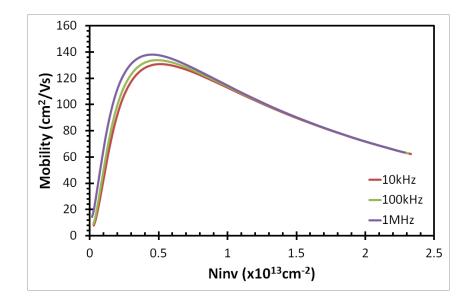

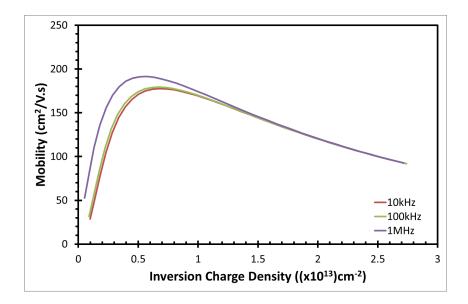

| 4.12 | Effective mobility extracted for wafer with rGe layers and $\rm Si_3H_8$               |    |

|      | passivation scheme. The measurements were taken at room                                |    |

|      | temperature                                                                            | 71 |

| 4.13 | Linear drain current taken for wafer with rGe layers and ${\rm SiH}_4$ |    |

|------|------------------------------------------------------------------------|----|

|      | passivation scheme. The measurements were taken at room                |    |

|      | temperature                                                            | 72 |

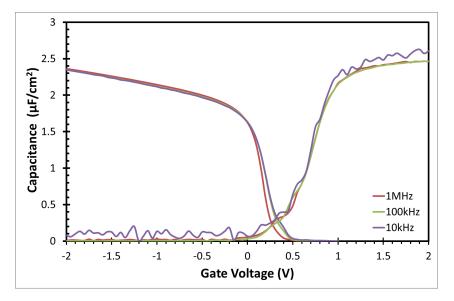

| 4.14 | Capacitance characteristics in function of frequency for wafer         |    |

|      | with rGe layers and $SiH_4$ passivation scheme. The measure-           |    |

|      | ments were taken at room temperature                                   | 72 |

| 4.15 | Effective mobility extracted for wafer with rGe layers and $SiH_4$     |    |

|      | passivation scheme. The measurements were taken at room                |    |

|      | temperature                                                            | 73 |

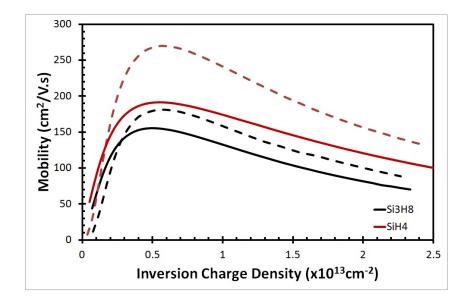

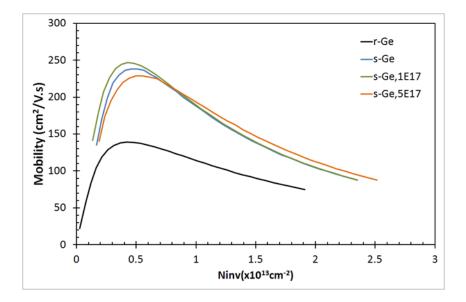

| 4.16 | Effective mobility in function of the inversion charge for devices     |    |

|      | with different passivation methods. Solid lines represent room         |    |

|      | temperature data and dashed lines represent data taken at 77 K.        | 74 |

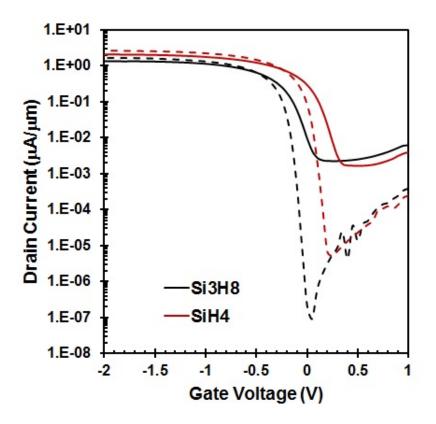

| 4.17 | Drain current as a function of gate voltage for devices with           |    |

|      | different passivation methods. Solid lines represent room tem-         |    |

|      | perature data and dashed lines represent data taken at 77 K            | 75 |

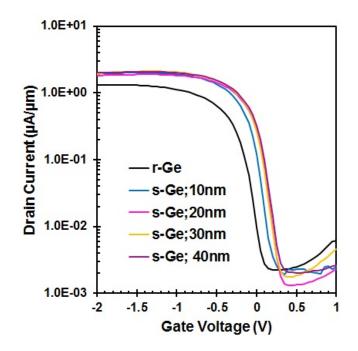

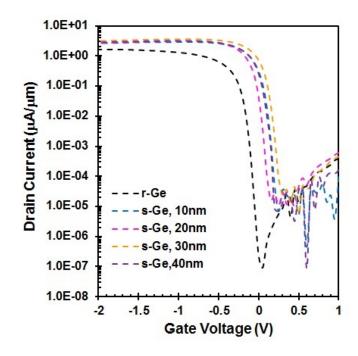

| 4.18 | Drain current for different channel thickness taken at room tem-       |    |

|      | perature                                                               | 76 |

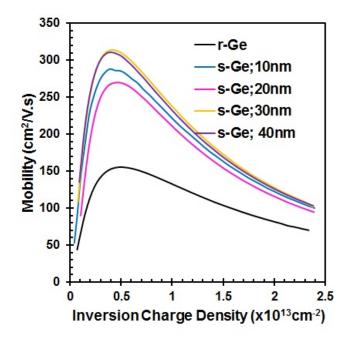

| 4.19 | Effective mobility for different channel thickness taken at room       |    |

|      | temperature                                                            | 77 |

| 4.20 | Drain current for different channel thickness at 77 K                  | 77 |

| 4.21 | Effective mobility for different channel thickness at 77 K             | 78 |

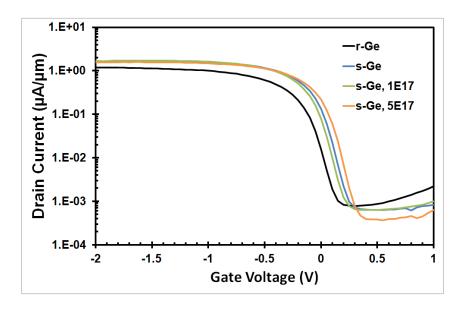

| 4.22 | Drain current for different doping concentrations taken at room        |    |

|      | temperature                                                            | 79 |

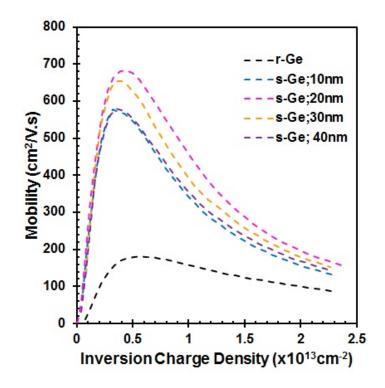

| 4.23 | Effective mobility for different doping concentrations taken at        |    |

|      | room temperature.                                                      | 80 |

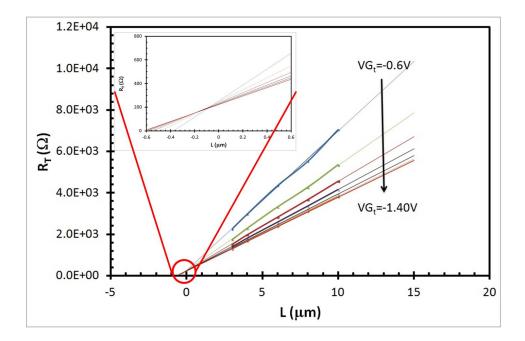

| 4.24 | Determination of series resistance by the method described in            |    |

|------|--------------------------------------------------------------------------|----|

|      | section 3.3.3.2                                                          | 81 |

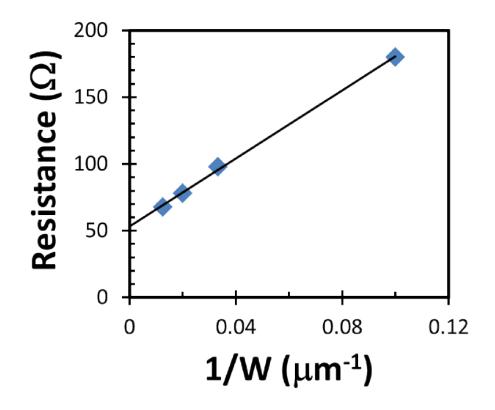

| 4.25 | Plot for series resistance determination from $W^{-1}$ method for        |    |

|      | devices in wafer D04 at room temperature                                 | 83 |

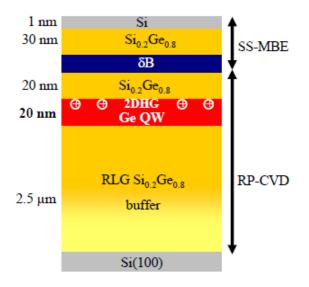

| 5.1  | Schematic diagram of sample 12-28                                        | 88 |

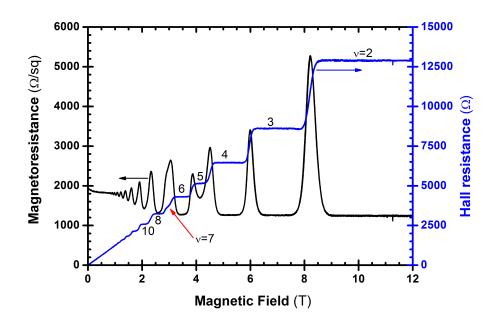

| 5.2  | Shubnikovde Haas and Quantum Hall Effects at a temperature               |    |

|      | of 316 mK                                                                | 89 |

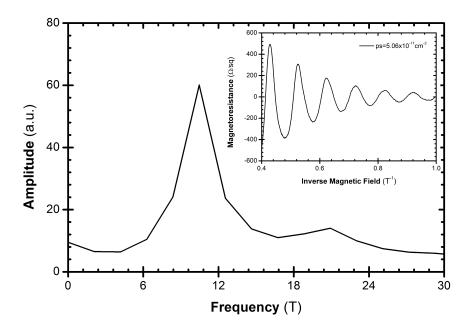

| 5.3  | SdH oscillations in inverse magnetic field (inset) and their FFT         |    |

|      | spectrum for sample 12-28 at 316 mK                                      | 89 |

| 5.4  | Magnetic field dependence of magnetoresistance and spin-splitting        |    |

|      | dependence with temperature                                              | 90 |

| 5.5  | Spin-splitting dependence on temperature with temperature.               | 91 |

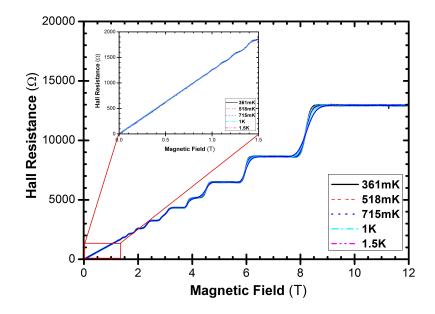

| 5.6  | Magnetic field dependences of Hall resistance measured at dif-           |    |

|      | ferent temperatures. In the inset is shown the linear region of          |    |

|      | the Hall resistance.                                                     | 92 |

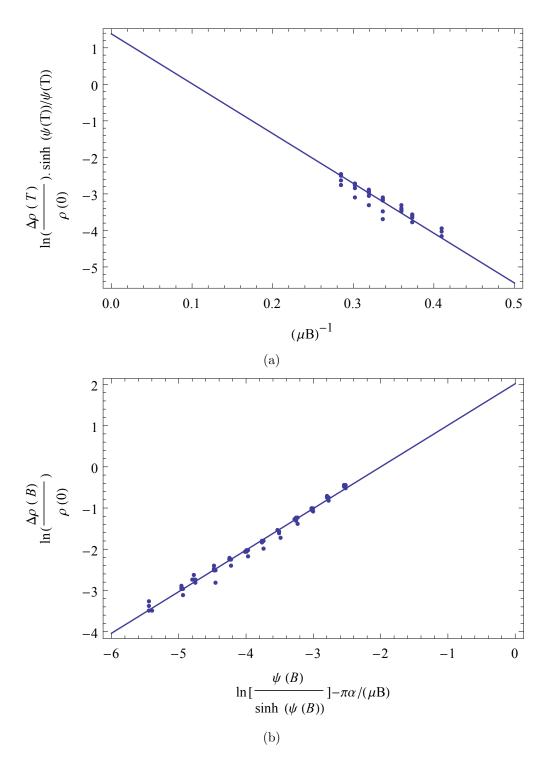

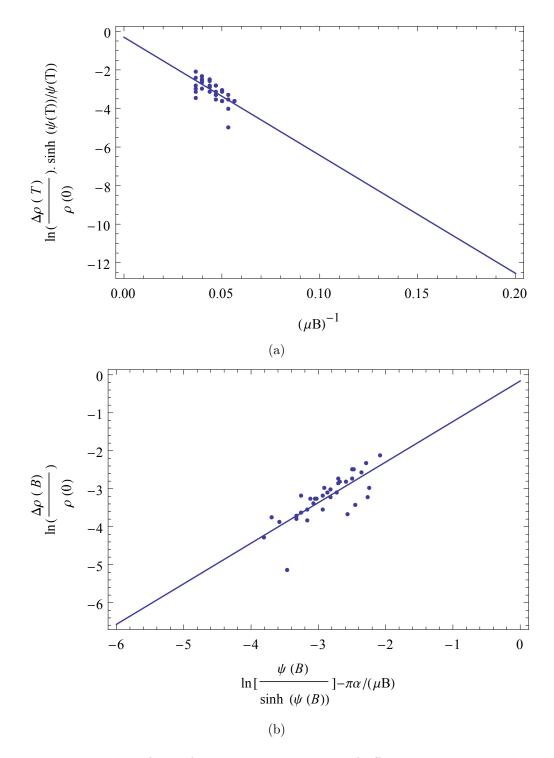

| 5.7  | Plots for self-consistent extraction of effective mass $m^*$ and pa-     |    |

|      | rameter $\alpha$ for different temperatures (a) and magnetic fields (b). | 93 |

| 5.8  | Schematic cross-section of sample 12-131                                 | 94 |

| 5.9  | Cross-section TEM of sample 12-447                                       | 95 |

| 5.10 | Hall bar fabricated for magnetoresistance measurements                   | 96 |

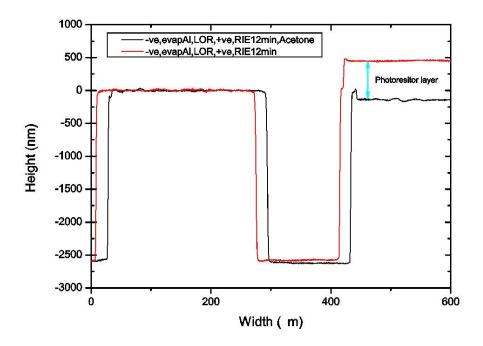

| 5.11 | Profilemeter graph after samples undergo dry etching                     | 97 |

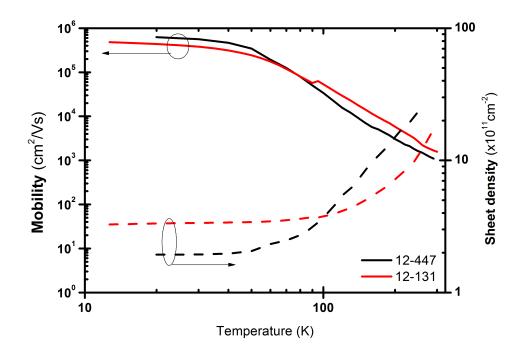

| 5.12 | Hall mobility (solid lines) and sheet density (dash lines) as a          |    |

|      | function of temperature for sample 12-131 and 12-447. Both               |    |

|      | samples were etched until the substrate                                  | 98 |

|      |                                                                          |    |

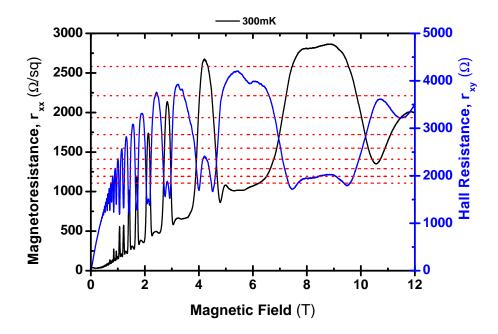

| 5.13 | Magnetic field dependences of magnetoresistance and Hall Re-             |      |

|------|--------------------------------------------------------------------------|------|

|      | sistance for a measurement at 300 mK. The landau levels are              |      |

|      | represented in red dotted lines                                          | 100  |

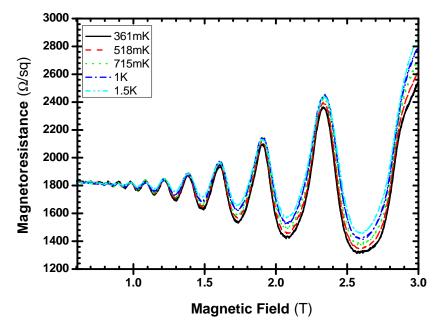

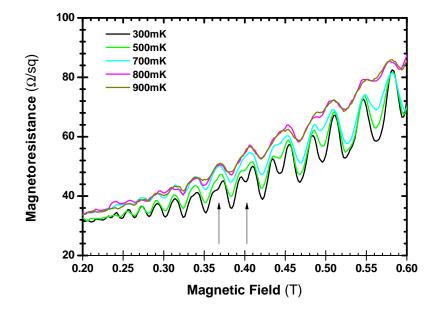

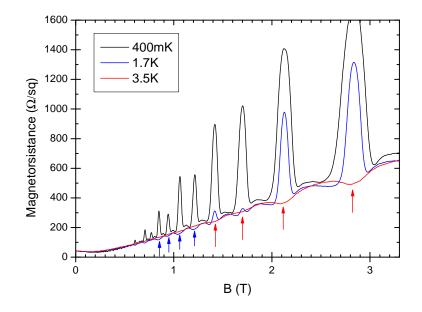

| 5.14 | Low field SdH oscilations for sample 12-447, measured at tem-            |      |

|      | peratures from 300 mK to 900 mK                                          | 101  |

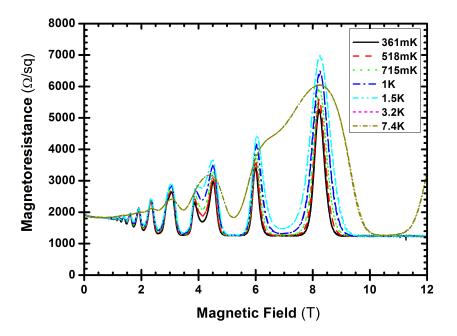

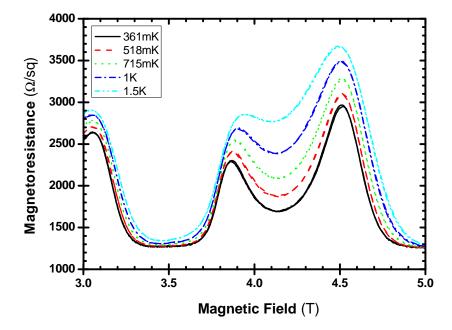

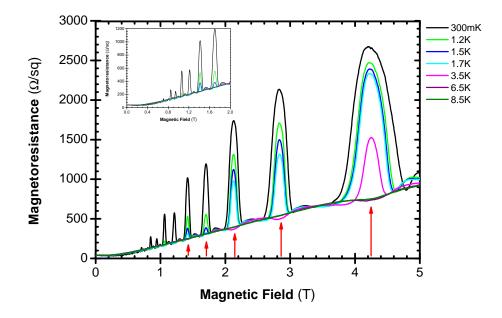

| 5.15 | Temperature dependence characteristics of the magnetoresis-              |      |

|      | tance, measured at different temperatures                                | 101  |

| 5.16 | Magnetoresistance of sample 12-447 at intermediate tempera-              |      |

|      | ture and field showing the emergence of peaks from SdH minima.           | .102 |

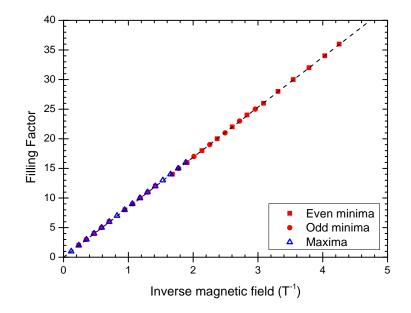

| 5.17 | Filling factor as a function of inverse magnetic field for sample        |      |

|      | 12-447. Filled points are taken at SdH minima (from a range of           |      |

|      | temperatures), open points are for peaks in resistivity seen at          |      |

|      | lowest temperature. The straight line through the origin shows           |      |

|      | that the filling factors have been correctly assigned                    | 103  |

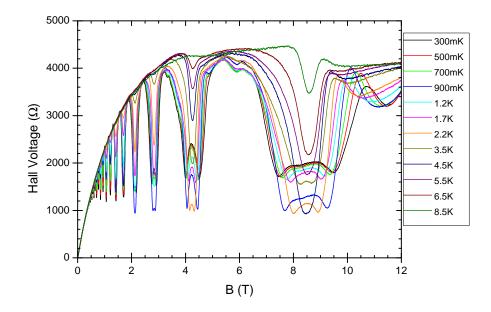

| 5.18 | Temperature dependence of the Hall resistance for sample 12-447.         | .104 |

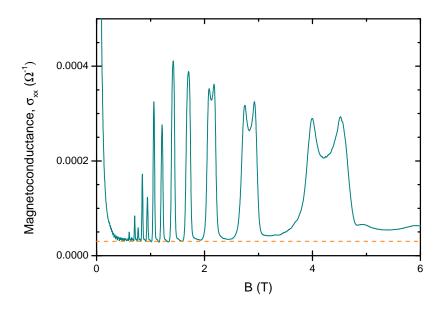

| 5.19 | Magnetoconductivity for sample 12-447 at 300 mK                          | 105  |

| 5.20 | Plots for self-consistent extraction of effective mass $m^*$ and pa-     |      |

|      | rameter $\alpha$ for different temperatures (a) and magnetic fields (b). | 106  |

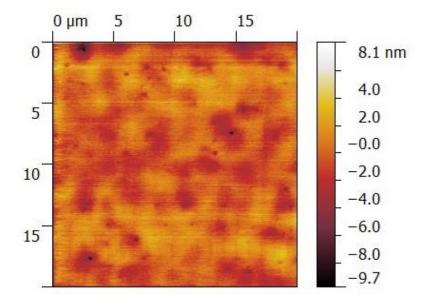

| 6.1  | An AFM schematic representation of the surface morphology of             |      |

|      | sample of Ge grown by CVD, prior to oxidation                            | 112  |

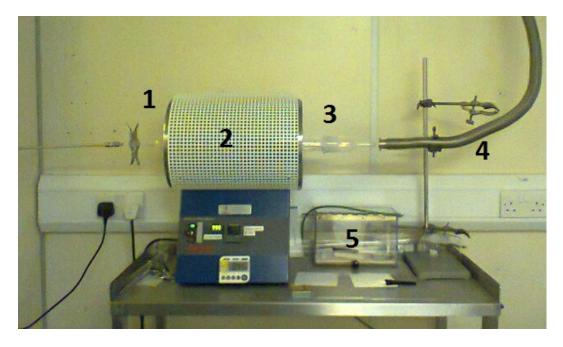

| 6.2  | System used to perform the oxidation. it is composed of an               |      |

|      | inlet for the gases (1), a furnace (2), a quartz tube (3), gases         |      |

|      | extraction tube (4) and box to storage the samples (5). $N_2$ is         |      |

|      | constantly passing through the box                                       | 114  |

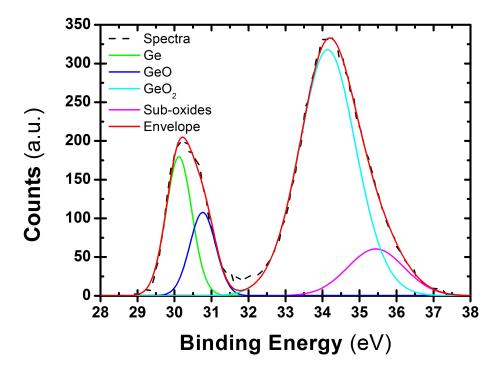

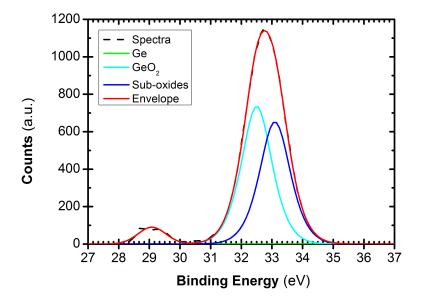

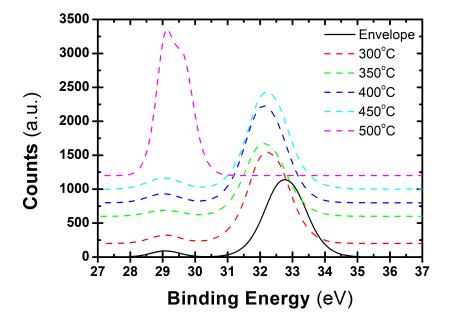

| 6.3  | XPS Ge $3d$ spectra for the sample with natural oxide as-grown           | 117  |

|      |                                                                          |      |

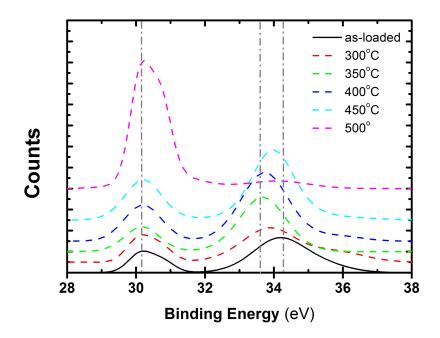

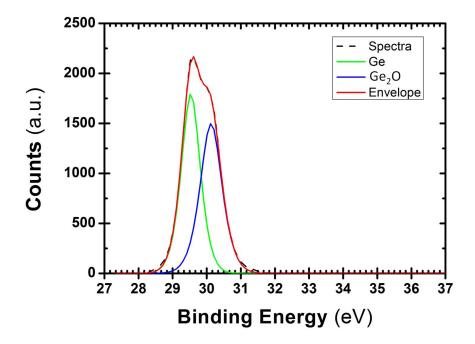

| 6.4  | XPS Ge $3d$ spectra for the sample with natural oxide as function                                                      |     |

|------|------------------------------------------------------------------------------------------------------------------------|-----|

|      | of annealed temperature                                                                                                | 118 |

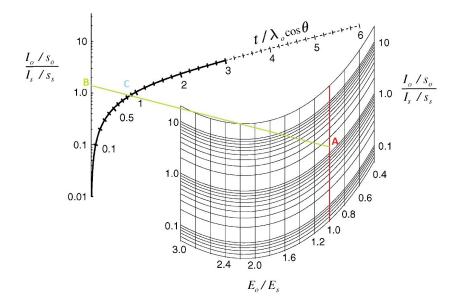

| 6.5  | Thickogram for determining the Germanium Oxide thickness.                                                              |     |

|      | The ratio of kinetic energy of overlayer and substrate peaks is                                                        |     |

|      | 1. The intensity ratios is 1.53. This gives an intersection for                                                        |     |

|      | C=0.9                                                                                                                  | 118 |

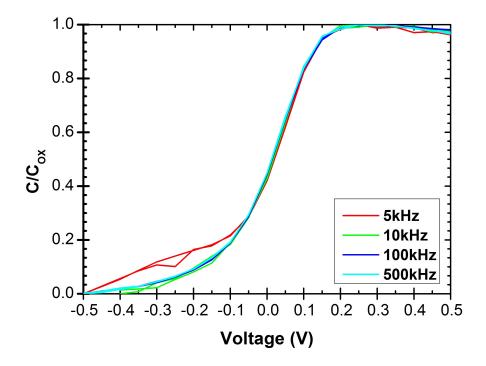

| 6.6  | C-V characteristics of $Al/GeO_2/Ge$ capacitors at frequencies of                                                      |     |

|      | 5k-500 kHz for samples grown at 450°C for an oxidation time of                                                         |     |

|      | 30 minutes. $N_D = 2.8 \times 10^{18} \text{ cm}^{-3}$ , $t_{ox} = 272.5 \text{ nm}$ as measured                       |     |

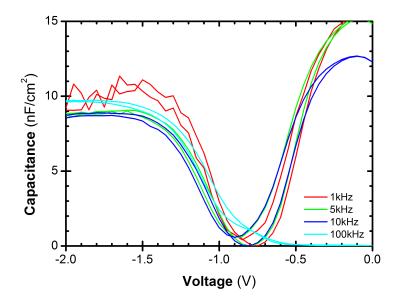

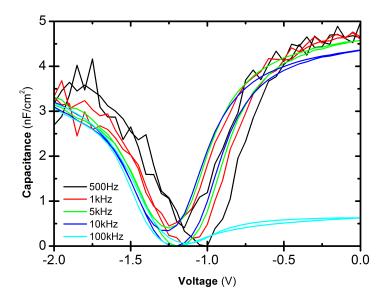

|      | by the CV curve.                                                                                                       | 119 |

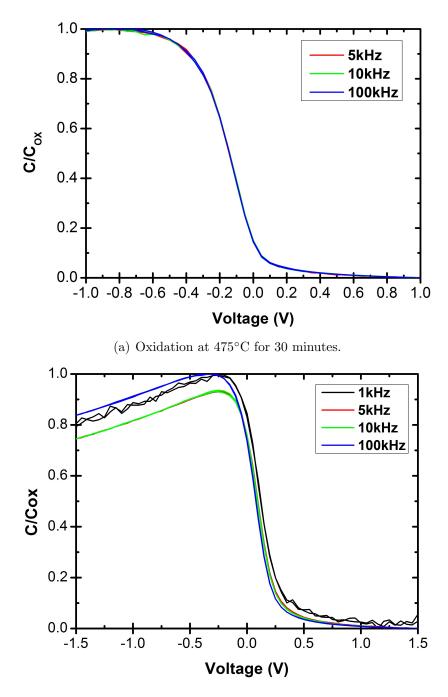

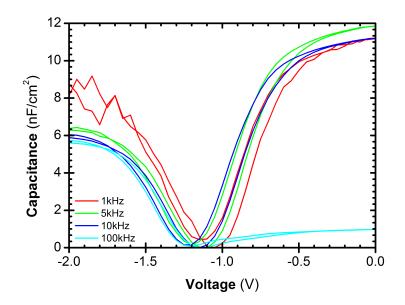

| 6.7  | C-V characteristics of $Al/GeO_2/Ge$ capacitors at frequencies of                                                      |     |

|      | 1k - 100 kHz for samples grown at: a) 475°C for 30 minutes,                                                            |     |

|      | $\mathrm{N}_A~=~4.5\times10^{15}~\mathrm{cm}^{-3},~\mathrm{t}_{ox}~=~58.4$ nm as measured by CV                        |     |

|      | curves; and b) at 475°C for 60 minutes, $N_A = 9.8 \times 10^{14} \text{ cm}^{-3}$ ,                                   |     |

|      | $t_{ox} = 47.9$ nm as measured by CV curves                                                                            | 120 |

| 6.8  | Oxidation at $450^{\circ}$ C for 30 minutes                                                                            | 122 |

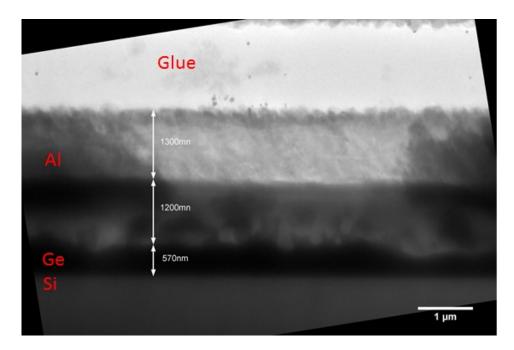

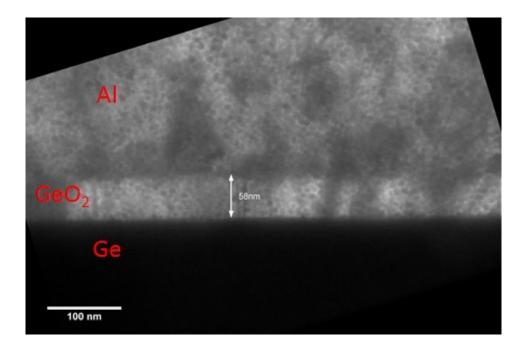

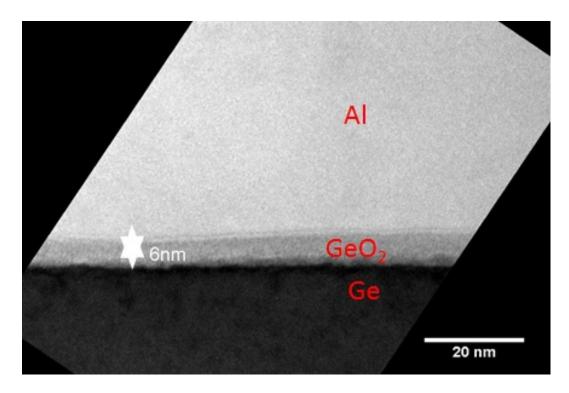

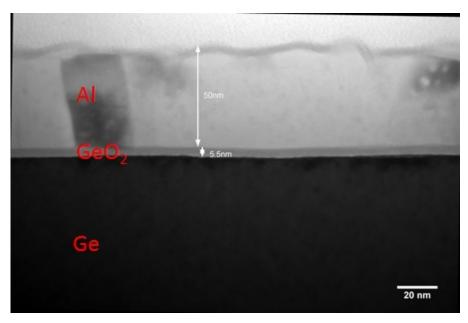

| 6.9  | Cross-sectional TEM images of the oxidized samples for samples                                                         |     |

|      | grown at 475°C for 30 minutes. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                            | 122 |

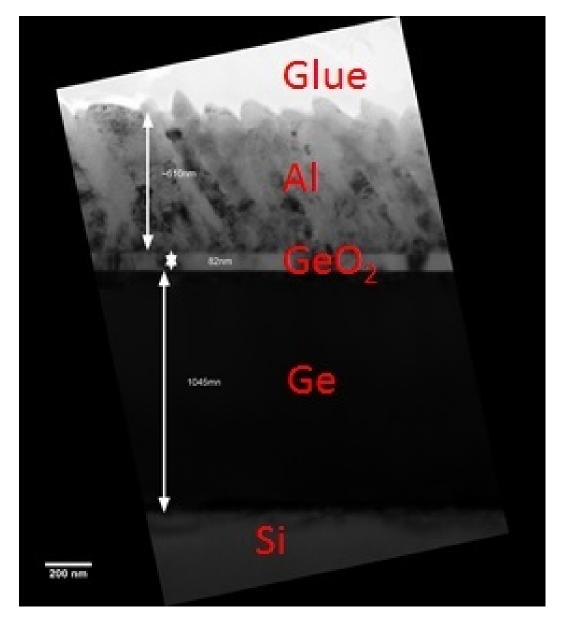

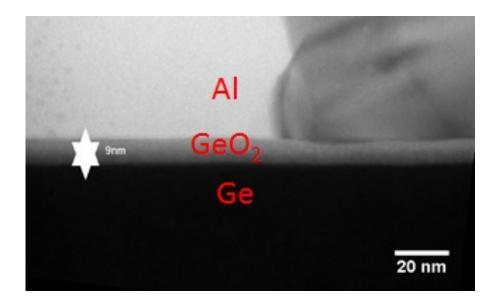

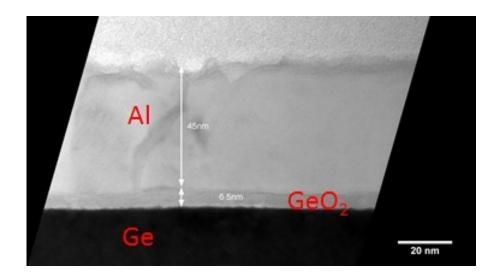

| 6.10 | Cross-sectional TEM images of the oxidized samples for samples                                                         |     |

|      | grown at $475^{\circ}$ C for 60 minutes                                                                                | 123 |

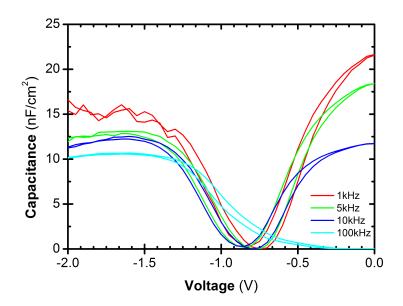

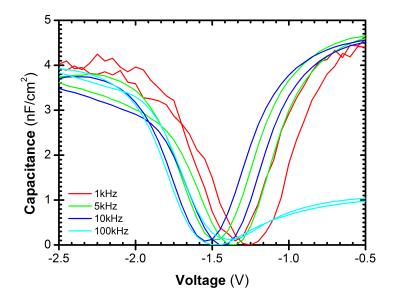

| 6.11 | C-V characteristics of $Al/GeO_2/Ge$ capacitors at frequencies of                                                      |     |

|      | 1k-100 kHz for samples grown at 500°C for 30 minutes. ${\rm N}_A =$                                                    |     |

|      | $4.7\times 10^{14}~{\rm cm}^{-3}, {\rm t}_{ox}=7.2$ nm as measured by CV curves                                        | 125 |

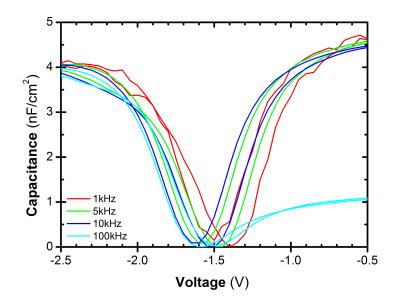

| 6.12 | C-V characteristics of $Al/GeO_2/Ge$ capacitors at frequencies                                                         |     |

|      | of $1k - 100$ kHz for samples grown at 500°C for 45 minutes.                                                           |     |

|      | $\mathrm{N}_A = 4.1 \times 10^{14} \ \mathrm{cm^{-3}},  \mathrm{t}_{ox} = 6.7 \ \mathrm{nm}$ as measured by CV curves. | 126 |

|      |                                                                                                                        |     |

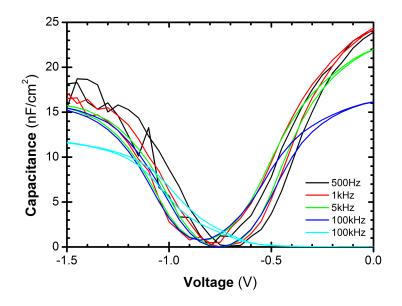

- 6.13 C-V characteristics of Al/GeO<sub>2</sub>/Ge capacitors at frequencies of 500 - 100 kHz for samples grown at 500°C for 60 minutes.  $N_A = 2.9 \times 10^{14} \text{ cm}^{-3}$ ,  $t_{ox} = 5.8 \text{ nm}$  as measured by CV curves. 126

- 6.14 C-V characteristics of Al/GeO<sub>2</sub>/Ge capacitors at frequencies of 500 - 100 kHz for samples grown at 550°C for 30 minutes.  $N_A = 1.3 \times 10^{14} \text{ cm}^{-3}$ ,  $t_{ox} = 8.7 \text{ nm}$  as measured by CV curves. 127

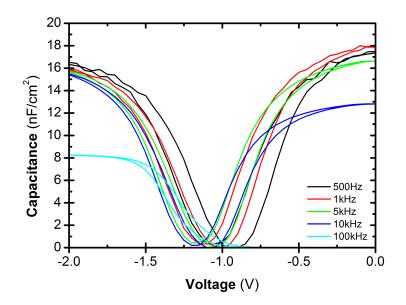

- 6.15 C-V characteristics of Al/GeO<sub>2</sub>/Ge capacitors at frequencies of 500 - 100 kHz for samples grown at 550°C for 45 minutes.  $N_A = 4.0 \times 10^{14} \text{ cm}^{-3}$ ,  $t_{ox} = 22.6 \text{ nm}$  as measured by CV curves. 127

- 6.16 C-V characteristics of Al/GeO<sub>2</sub>/Ge capacitors at frequencies of 1k - 100 kHz for samples grown at 600°C for 15 minutes.  $N_A = 4.2 \times 10^{14} \text{ cm}^{-3}$ ,  $t_{ox} = 13.0 \text{ nm}$  as measured by CV curves 128

- 6.17 C-V characteristics of Al/GeO<sub>2</sub>/Ge capacitors at frequencies of 1k - 100kHz for samples grown at 600°C for 30 minutes.  $N_A = 6.8 \times 10^{14} \text{ cm}^{-3}$ ,  $t_{ox} = 11.9 \text{ nm}$  as measured by CV curves 128

- 6.18 C-V characteristics of Al/GeO<sub>2</sub>/Ge capacitors at frequencies of 1k - 100kHz for samples grown at 600°C for 45 minutes.  $N_A = 5.6 \times 10^{14} \text{ cm}^{-3}$ ,  $t_{ox} = 17.0 \text{ nm}$  as measured by CV curves 129

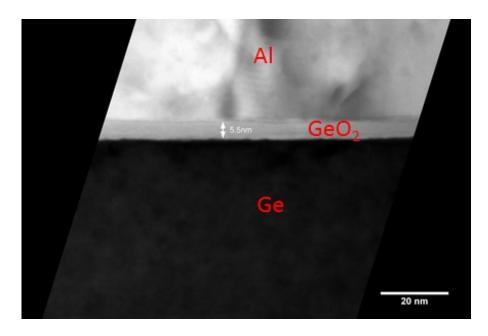

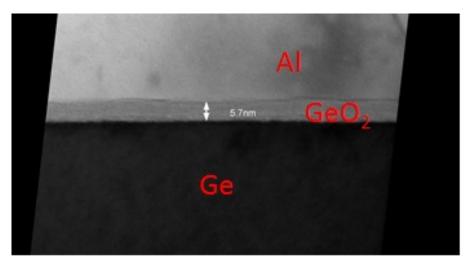

- 6.22 Cross-sectional TEM images of the sample oxidized at 550°Cfor 30 minutes.133

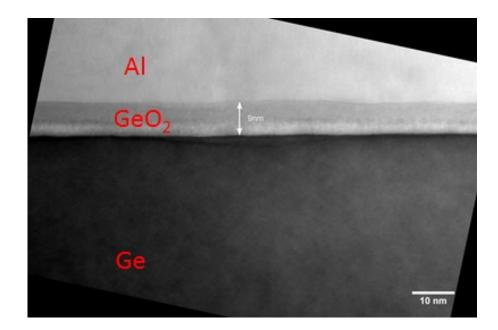

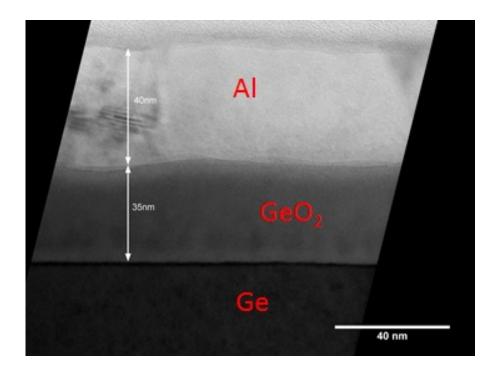

| 6.23 Cross-sectional TEM images of the sample oxidized at $550^\circ\mathrm{C}$        |     |

|----------------------------------------------------------------------------------------|-----|

| for 45 minutes.                                                                        | 133 |

| $6.24$ Cross-sectional TEM images of the sample oxidized at $600^o\mathrm{C}$          |     |

| for 15 minutes.                                                                        | 134 |

| $6.25$ Cross-sectional TEM images of the sample oxidized at $600^\circ\mathrm{C}$      |     |

| for 30 minutes.                                                                        | 134 |

| $6.26$ Cross-sectional TEM images of the sample oxidized at $600^\circ\mathrm{C}$      |     |

| for 45 minutes.                                                                        | 135 |

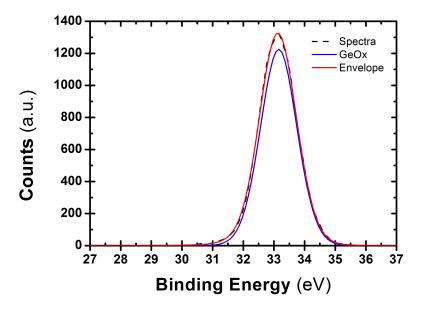

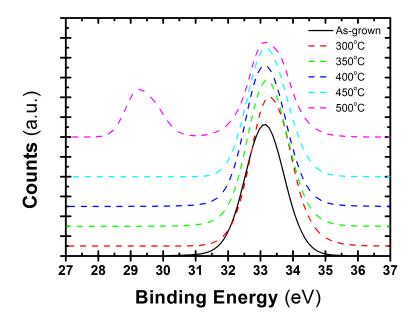

| $6.27$ XPS Ge $3d$ spectra for the as-grown sample oxidized at $500^{\circ}\mathrm{C}$ |     |

| for 45 minutes.                                                                        | 135 |

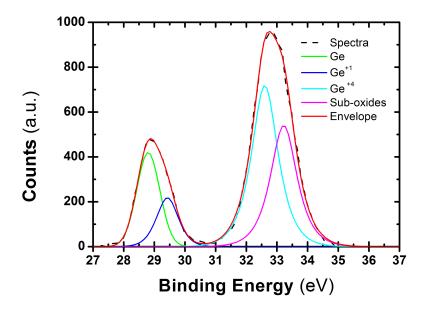

| 6.28 XPS Ge $3d$ spectra for sample oxidized at 500°C for 45 minutes                   |     |

| after annealing at 500°C                                                               | 136 |

| 6.29 XPS Ge $3d$ spectra for the as-grown sample oxidized at 550°C                     |     |

| for 30 minutes.                                                                        | 136 |

| 6.30 XPS Ge $3d$ spectra for the sample oxidized at 550°C for 30                       |     |

| minutes after annealing at 550°C                                                       | 137 |

| 6.31 XPS Ge $3d$ spectra as function of anneal temperature for sam-                    |     |

| ples oxidised at 500°C for 45 minutes                                                  | 138 |

| 6.32 XPS Ge $3d$ spectra as function of anneal temperature for sam-                    |     |

| ples oxidised at 550°C for 30 minutes                                                  | 138 |

### Acknowledgments

This thesis would not be possible without the help of a number of people. First of all, I would like to thank my supervisors Prof. David Leadley and Dr. Maksym Myronov for all the help and guidance through this work.

The development of this work would have not been possible without several other members of the Nano-Silicon group past and present. I would like to thank Dr Andy Dobbie for introducing me to our labs and research. I would also like to thank Prof. Evan Parker and Prof. Terry Wall for their advice and supervision. I would like to thank Dr. Vishal Shah for is patience in teaching me and answer all my questions. During my time in the lab I realised I had a gift for breaking, for this reason I frequently need the help of Tim Naylor, Alistair Julian and Dr. Alan Burton, so I would like to thank them for all their help. I want to thank also to Dr Chris Morrison, Dr Martin Prest and Dr. Stephen Rhead for their help. Our lunch time was always a time of learning, my English has improved considerably due the teachings of James, Jamie, Phil and Dave.

A special thanks goes to Amna Hassan, I'll always remember our late nights in the lab doing measurements together as well as our tea brakes where we talk about everything and anything. Another special thank goes to John Halpin who has been a friend in all occasions, from our first year in the office, where we worked but also found time for our discussions on different topics, to my last year helping me and encouraging me to finish this thesis.

My passage by Warwick would not have been the same without the presence of Nessa, Natalia, Priyanka, Assma and Manuel, thank you for all the support and friendship. I would like to thank also my housemates Yan, Alice, Carol, Mayada and Clara for your friendship, you made our house a very good house. You are all my support group away from home.

In my corner it has always been my friends Sónia and Di, that even far away always gave their support and encouragement through email, phone calls and Skype calls when I needed the most. I don't have the words to thank you girls.

Um agradecimento muito especial vai para os meus pais que sempre me apoiaram em todas as minhas loucuras, incluindo esta. Sem a vossa ajuda e apoio não teria conseguido. Um agradecimento especial vai também para o meu irmão Sérgio e para a minha cunhada Fátima pelo vosso apoio. Também gostaria de agradecer ao meu sobrinho Miguel por ser capaz de sempre me deixar com um sorriso.

# Declarations

This thesis is submitted to the University of Warwick in support of my application for the degree of Doctor of Philosophy. It has not been submitted for a degree at any other University.

All of the work described in this thesis was carried out by the author, or under her direction, in the Department of Physics at the University of Warwick except in the following cases:

- The AFM and TEM images were taken by John E. Halpin.

- The XPS spectra were taken by Dr. Marc Walker and James Mudd.

# Abstract

With continued scaling down of devices it is necessary to look into new materials in order to improve device performance. Ge and SiGe are good candidates for channel materials since they present high carrier mobility. Also, in order to reduce the gate leakage as the dielectric thickness is reduced it is necessary to look at high- $\kappa$  materials to substitute the Si-SiO<sub>2</sub> as it reaches its limits. This thesis investigates different properties of Ge devices.

The first part of this work investigates Ge channel MOSFETs and the effects of different growth parameters such as Ge surface passivation scheme, channel thickness and doping concentration on device performance. It is shown that, for these devices, strain can provide a 50% increase in mobility, but channel thickness and doping concentration do not show significant enhancement in mobility.

The second part looks at the transport properties of very high mobility, strained Ge channel, modulation doped devices. A mobility of around  $7 \times 10^5 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  was measured at 300 mK for a Ge heterostructure grown by CVD. Values for the hole effective mass of  $0.083 \pm 0.002 m_0$  were obtained from the temperature and field dependence of Shubnikov-de Hass oscillations in the magnetoresistance.

In the last chapter, developments on thermal growth of  $\text{GeO}_2$  are investigated using a simple oxidation process. It is shown that this process demonstrates good device characteristics and a smooth Ge-GeO<sub>2</sub> interface. For devices under study an interface trap density around  $10^{11} \text{eV}^{-1} \text{cm}^{-2}$  is estimated using the low-high frequency method.

# **Publications**

#### 0.1 Publications

M. Myronov, C. Morrison, *C. Casteleiro*, J. Foronda, S. Rhead, D.R. Leadley

"Ground breaking room-temperature mobility of 2D holes in a strained Ge quantum well heterostructures grown by Reduced Pressure Chemical Vapor Deposition"

Int. Conf. on Solid State Devices and Materials (SSDM) Sept 24-27, Fukuoka, Japan. 2013

C. Casteleiro, J. E. Halpin, V. A. Shah, M. Myronov, D. R. Leadley, "'Thermally grown GeO2 on epitaxial Ge on Si(001) substrate."'

Intl Conf on Ultimate Integration on Silicon (ULIS-14) Warwick, March 2013

J. Jasiński, L. Łukasiak, A. Jakubowski, C. Casteleiro, T. E. Whall, E. H. Parker, M. Myronov, D. R. Leadley,

"'Influence of series resistance determination on the extracted mobility in MOS transistors with Ge channel."'

Submitted in SPIE proceedings

#### 0.2 Participations/attendance in Conference

2013 $8^{th}$  International Conference on Silicon Epitaxy and Heterostructures -  ${\bf Poster}$  presentation

Electrical and Structural Characterization of Thermally Grown GeO2 on Epitaxial Ge on a Si(001) Substrate

2013 $14^{th}$  International Conference on Ultimate Integration on Silicon -  ${\bf Poster}$  presentation

Thermally grown GeO2 on epitaxial Ge on Si(001) substrate.

2012 Condensed Matter and Materials Physics Conference **Poster** presentation

Electrical and structural properties of thermally grown GeO2 on epitaxial Ge on Si(001) substrate

2012 $13^{th}$  International Conference on Ultimate Integration on Silicon

2011 Condensed Matter and Materials Physics Conference - **Poster** presentation

Study of the effect of channel thickness and Si cap passivation on hole mobility of strain Ge pMOSFETs

2010 Condensed Matter and Materials Physics Conference - **Poster** presentation

Effective hole mobility in relaxed and strained Ge Channel transistor

2009 Condensed Matter and Materials Physics Conference

### Chapter 1

# Introduction

#### 1.1 Motivation

Gordon Moore (Intel's co-founder) predicted, in 1965, that the number of transistors on a chip would double every year [1] which became known as Moore's Law. This law has been the driving force behind the scaling down of devices, in particular the metal-oxide-semiconductor-field-effect transistors (MOSFET) that underpin the whole electronics industry through complimentary MOS (CMOS) circuitry. Between each 'technology node' devices have been scaled by a factor  $\kappa$ , which according to Moore's law is 2. The parameters to be scaled are device dimensions (oxide thickness, width and channel length and junction depth), by a factor of  $1/\sqrt{\kappa}$ , substrate doping concentration by  $\kappa$ , and supply voltage by  $1/\sqrt{\kappa}$  [2].

Initially, this scaling was simply performed by taking advantage of developments in the fabrication process, in the main through advances in lithography techniques. However, in order to maintain the enhancements in performance it has become necessary to look at new materials, and to develop novel interface systems and alternative gate concepts, whilst still maintaining compatibility with silicon based-technologies [3]. Although the first transistor was made of germanium (Ge), silicon (Si) is the main component in device fabrication mainly due to the good quality of the interface of Si with is natural oxide, silicon dioxide, SiO<sub>2</sub> and it is abundant therefore cheaper. Ge, on the other hand, is not abundant and does not possess a good interface with its natural dielectric, GeO<sub>2</sub>. Also, since the melting point of Ge, 937° C, is lower than for Si, a smaller thermal budget can be used for CMOS processing. Nevertheless, Ge is again being considered to be a good candidate for future MOSFETs, as it has a higher bulk mobility being more than 4 times that of Si for holes and 2 times for electrons. The principal aim of this thesis is to explore the possibilities offered by Ge channel devices and how these can be realised in practice.

Ge channel MOSFETs are already a reality, presenting good results for both n-channel and p-channel [4–7]. Because of the narrower band gap, devices made with a Ge and/or SiGe channel present higher junction leakage current, which is a concern for low power applications. Also, Ge presents a channel orientation dependency due to the anisotropy of the hole effective mass. In scaling down the SiO<sub>2</sub> layer used within the MOSFET gate stack to a few monolayers, the gate leakage current increases which consequently leads to devices degradation. Replacing the SiO<sub>2</sub> with a high- $\kappa$  dielectric can allow the physical oxide thickness to be increased while maintaining a low equivalent oxide thickness (EOT). In order to integrate high- $\kappa$  dielectrics it is necessary to take account a range of factors, such as the dielectric permittivity, oxide to semiconductor barrier height, gate metal work function, charge trapping in the oxide, as well as the effect on transport within the semiconductor channel of the oxide-semiconductor interface. A high dielectric permittivity element is associated with a low band gap and consequently lower barrier heights, which are responsible for the tunnelling process. There will be a trade-off between all these parameters, but for a practical MOSFET, the high- $\kappa$  dielectric constant should be between 10 to 30, the band offset should be above 1eV also, in order to attain a good electrical interface it is necessary for the high-k dielectric to be thermally stable for thermal budget temperatures, that is, 1000K for 90s [8, 9].

Another promising route for higher performing devices has been to develop III-V compounds for the n-type devices in CMOS, because of their high electron mobilities, for example 77,000  $\text{cm}^2/\text{Vs}$ , 40,000  $\text{cm}^2/\text{Vs}$ , 9,200  $\text{cm}^2/\text{Vs}$ and  $5,400 \text{ cm}^2/\text{Vs}$  for indium antimonide (InSb), indium arsenide (InAs), gallium arsenide (GaAs) and indium phosphorus (InP), respectively. The enhancement factor in electron mobility compared to Si can reach 50 in the bulk [10]. However, the integration of III-V devices with silicon infrastructure, while maintaining the same quality, is not easy. Problems start with the high cost of III-V substrates and the fact that these are simply not available at the sizes used for silicon mass production (now 450 mm diameter). In addition, there are difficulties with both the epitaxial growth of III-Vs directly on Si and with a layer transfer/wafer bonding approach. Epitaxial growth is difficult because of the high lattice mismatch between Si and the III-Vs, which means a high dislocation density. Consequently, an additional strain-tuning buffer layer is required, for which Ge-on-Si is a possible candidate because of the closer lattice match to GaAs. On the other hand, integration via bonding has problems concerning damage to the conducting channel, caused during the  $H^+$  implants, and a mismatch of the thermal coefficients of expansion, which leads to wafers bowing and/or cracking during the bonding process. A combination of the two developments just mentioned, that is, co-integration of III-V n-type and Ge p-type devices on the same Ge-on-Si platform may provide the ultimate solution for high performance CMOS [11, 12].

#### 1.2 Basic properties of Si and Ge

Both Si and Ge are group-IV elements that crystallize in the diamond lattice and have an indirect band gap, with silicon having the largest ( $E_{g_{Si}} =$ 1.12 eV and  $E_{g_{Ge}} = 0.66$  eV). In Si, the conduction band minima lie in the [100] direction ( $\Delta$  minima) and are sixfold degenerated, whereas in Ge they are in the [111] direction (L minima) and are eightfold degenerated [2, 13–16], see Figure 1.1. The valence band minima,  $\Gamma$ -point, consists of three bands: i) heavy-hole (HH) band, ii) light-hole (LH) band and iii) a split off band due to spin-orbit interaction. The effective mass,  $m^*$  depends on the crystal direction. When compared with Si, Ge possess a lower hole effective mass and has longer relaxation times, which can explain the higher mobilities encountered for Ge. Table 1.1 shows the basic properties of selected semiconductors.

Si and Ge are the only group IV elements that are miscible across the alloy composition range. Si can be combined with Ge to form an alloy of  $\operatorname{Si}_{1-x}\operatorname{Ge}_x$ , where x represents the Ge composition and takes values between 0 < x < 1, still with the diamond lattice structure. On changing x the alloy characteristics are changed, such as the lattice parameter and band gap value. Figure 1.2 shows how the band gap of the alloy varies with Ge content. Although the lowest lying conduction band changes from the  $\Delta$ -valley to the L-valley once x exceeds 0.85, the band gap of SiGe alloys remains indirect for all compositions.

|                                                    | Si                                 | Ge                                                        | GaAs                               | InP                           | InAs                          | InSb                           |

|----------------------------------------------------|------------------------------------|-----------------------------------------------------------|------------------------------------|-------------------------------|-------------------------------|--------------------------------|

| Lattice constant<br>at $300 \text{ K}(\text{\AA})$ | 5.43095                            | 5.64613                                                   | 5.6533                             | 5.8686                        | 6.0584                        | 6.4794                         |

| Crystal Structure                                  | Diamond                            | Diamond                                                   | Zincblende                         | Zincblende                    | Zincblende                    | Zincblende                     |

| Band Gap (eV)                                      | 1.12                               | 0.66                                                      | 1.42                               | 1.34                          | 0.36                          | 0.17                           |

| Permittivity                                       | 11.8                               | 16                                                        | 12                                 | 12.6                          | 14.8                          | 17                             |

| Electron mobility $(cm^2/Vs)$                      | 1600                               | 3900                                                      | 9200                               | 5400                          | 40000                         | 77000                          |

| Electron effective<br>mass (/mo)                   | ${ m m}_t:\!0.19 { m m}_l:\!0.916$ | $\mathrm{m}_t$ :0.0082 $\mathrm{m}_l$ :1.467              | 0.067                              | 0.082                         | 0.023                         | 0.014                          |

| Hole mobility $(\text{cm}^2/\text{Vs})$            | 430                                | 1900                                                      | 400                                | 200                           | 500                           | 850                            |

| Hole effective<br>mass (/mo)                       | $m_{HH}$ :0.49 $m_{LH}$ :0.16      | $m_{HH}$ :0.28 $m_{LH}$ :0.044                            | $m_{HH}$ :0.045<br>$m_{LH}$ :0.082 | $m_{HH}$ :0.45 $m_{LH}$ :0.12 | $m_{HH}$ :0.57 $m_{LH}$ :0.35 | $m_{HH}$ :0.44 $m_{LH}$ :0.016 |

|                                                    | Table 1.1: Ba                      | Table 1.1: Basic parameter of Semiconductors [10, 17, 18] | of Semicondu                       | ctors [10, 17,                | 18]                           |                                |

Figure 1.1: Energy band structure for Ge (left) and Si (right). Reproduced from [2].

The lattice parameter of the alloy follows Kasper-corrected-Vegard's law, which states that the increase of lattice parameter with x follows equation 1.1 [15, 19].

$$a_{Si_{1-x}Ge_{x}} = a_{Si} \cdot (1-x) + a_{Ge} \cdot x - 0.00273x(1-x) \tag{1.1}$$

where the lattice parameters for Si and Ge,  $a_{Si} = 0.5431$  nm and  $a_{Ge} = 0.5658$  nm, differ by 4.2%. This is a linear interpolation between both lattice parameters [20]. As can be seen in Figure 1.2, the band gap of the alloy decreases with increasing Ge content, although it does not change linearly and there is an additional bowing parameter which makes a significant difference for the bulk alloy.

Figure 1.2: Variation of band gap of  $\operatorname{Si}_{1-x}\operatorname{Ge}_x$ , with Ge content x. At x=0.85 it is possible to observe the alloy crossover from the Si-like to Ge-like band structure for unstrained layers (top curve). For strain layers (bottom curves) is depicted the valence band splitting. Taken from [15]

#### **1.3** Strained layers

Figure 1.2 also shows the resulting band gap for  $\operatorname{Si}_{1-x}\operatorname{Ge}_x$  on Si for a range of x. It can be seen that there are now two lines for the band gap, since the degeneracy between heavy holes (HH) and light holes (LH) at the zone centre is lifted by the strain, with the heavy hole band being displaced upwards. This is very important for charge transport in Ge because the scattering rate for holes in the strained system is much less by having a reduced density of states to scatter into. Furthermore, the strain also distorts the shape of the hole bands which leads to a lighter effective mass for HHs under compressive strain, again improving their transport properties and leading to an increase in the hole mobility [13, 14, 21].

In addition to the changes in material characteristics caused by alloying, further desirable changes can be achieved by straining the material. The 4.2% difference in lattice parameter between Si and Ge means that a thin epitaxial alloy layer grown pseudomorphically on a silicon substrate, i.e. retaining the same in-plane lattice spacing in the epitaxial overlayer as the underlying material, will be under biaxial compressive strain.

Figure 1.3: Critical thickness as a function of Germanium composition on a SiGe alloy grown on Si. Both the theoretical limit and the experimental curve for a metastable layer grown by MBE are shown. Reproduced from [15].

There is a limit to the amount of strain energy that can be built up in an epilayer before relaxation occurs through the nucleation of dislocations in the crystal [22–24]. Dislocations have a misfit segment that runs parallel to the heterointerface, which serves to accommodate the lattice difference, and also threading dislocations that can run up through the epilayer to terminate on the free surface. Threading dislocations are potentially very bad for device properties as they can provide a leakage path and so their density must be minimised, or avoided entirely by keeping the layer below the critical thickness. For Ge grown directly on Si the critical thickness would be only a couple of nanometres (see Figure 1.3), which would make device processing impossible as this layer would be entirely removed in the first cleaning step. Instead, fully strained Ge layers that are thick enough to process devices on can be grown on a relaxed Si<sub>1-x</sub>Ge<sub>x</sub> 'virtual substrate' [25–31].

It is also possible to produce Ge layers that are thicker than the critical thickness, by growing in perfectly clean conditions and at sufficiently low temperature so that there are no nucleation sites and insufficient thermal energy for dislocations to appear. Such layers are in a metastable state, which means they may start to relax if subject to further thermal processing so care for the overall thermal budget is needed [22].

#### **1.4** Ge surface passivation

A major concern when implementing high- $\kappa$  materials is the Ge-high- $\kappa$ interface quality. To optimise this it is necessary to correctly passivate the Ge surface. Several methods have been used to passivate the surface [8] such as Si-based methods, sulphur, nitridation, and GeO<sub>2</sub>. Common high- $\kappa$  dielectrics used are HfO<sub>2</sub>, ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> and GeO<sub>2</sub> the native oxide. The majority of the dielectrics used have oxygen in their composition, which forms an interlayer (IL) of GeO<sub>2</sub>, and it has been shown that this IL is responsible for improving device characteristics [32–34].

Sulphur passivation presented the worst results, not showing any en-

hancement in the interface trap density, the lowest value obtained was  $4.8 \times 10^{11} \text{ cm}^{-2} \text{eV}^{-1}$ , which is at least an order of magnitude too large for practical devices.

|                             | $\kappa$ |

|-----------------------------|----------|

| $\mathrm{SiO}_2$            | 3.9      |

| $\mathrm{Si}_3\mathrm{N}_4$ | 7        |

| $Al_2O_3$                   | 9        |

| $Ta_2O_5$                   | 22       |

| $\mathrm{TiO}_2$            | 80       |

| $\rm SrTiO_3$               | 2000     |

| $\rm ZrO_2$                 | 25       |

| $\mathrm{HfO}_{2}$          | 25       |

| $\mathrm{HfSiO}_4$          | 11       |

| $La_2O_3$                   | 30       |

| $Y_2O_3$                    | 15       |

| $a-LaAlO_3$                 | 30       |

| $\mathrm{GeO}_2$            | 5-6      |

|                             |          |

Table 1.2: Dielectric constant of candidate gate dielectrics. Taken from [35].

According to Chui *et al.* [36, 37] nitridation of Ge oxides lowers the interface trap density which can be reduced even further by annealling in forming gas. However, this presents an abnormal behaviour of the gate leakage due to charge trapping. Similarly, nMOSFETs treated in this way showed poor electrical characteristics, although the electrical characteristics could be improved by controlling the nitrogen concentration and the GeON thickness [38, 39]. It was found that a GeON IL, with a low N/Ge ratio, could reduce the deterioration caused by atomic laser deposition (ALD), a  $D_{it}$  of  $4 \times 10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> was obtained.

Si passivation consists of growing a thin Si cap on top of the Ge and SiGe surfaces. The Si cap reduces the gate leakage current, reduces the subthreshold slope (SS) and can enhance drive current, which leads to an improvement in the mobility of Ge devices [33, 40–43]. The Si cap can be grown using two precursors,  $SiH_4$  and  $Si_3H_8$ , which will be examined in some detail in Chapter four.

More recently, the interest in  $\text{GeO}_2$  as a passivation layer has increased. In order to passivate the surface several methods have been used, such as high pressure oxidation (HPO) [44], with and without low temperature oxidation annealing (LOA). The GeO<sub>2</sub> layer can also be grown by ozone oxidation [45], thermal oxidation [46], electron-cyclotron-resonance (ECR) plasma irradiation [47] and by direct growth on Ge substrates [48, 49]. A more detail description on different passivation methods will be given in Chapter six. Table 1.2 shows dielectric constants of candidate gate dielectrics.

#### 1.5 Thesis outline

This thesis will look into the effects of different growth conditions and device fabrication processes on Ge devices. In chapter two a brief description of concepts needed to understand this investigation is provided. Chapter three introduces the experimental techniques and data analyses techniques used to characterise the devices. The effects of Si cap growth, doping and channel thickness in relaxed and strained Ge MOSFETs are investigated in chapter four. In chapter five, results of magneto-transport measurements performed on a 2DHG in a strained Ge quantum well will be shown. Chapter six will describe thermally grown GeO<sub>2</sub> on epitaxial Ge-on-Si(100) substrates. Finally, in chapter seven, a summary of the main conclusions will be given as well as an outlook on further work.

### Chapter 2

## **Theoretical Background**

In this chapter an overview is presented of the theory necessary to perform and interpret the experiments and their results. In the first two sections a description will be given of the operation modes of MOS capacitors and MOSFETs.

#### 2.1 Metal-Oxide-Semiconductor capacitors

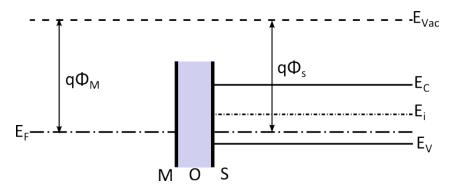

A metal oxide semiconductor (MOS) capacitor consist of a metal layer (gate) on top of a dielectric grown or deposited on a semiconductor body or substrate, see Figure 2.1.

Figure 2.1: Schematic of a Metal-Oxide-Semiconductor capacitor with the back contact present. The semiconductor can be n- or p-type. The metal gate act as a gate for the device.

The substrate is usually grounded and the gate can be biased with a voltage,  $V_G$ . The substrate can be doped n-type (pMOS capacitor) or p-type (nMOS capacitor). MOS capacitors are relatively simple devices to fabricate and to measure which provide useful information about the properties of a gate stack and channel that would be obtained after a full transistor fabrication process, but with some hundred fewer processing steps.

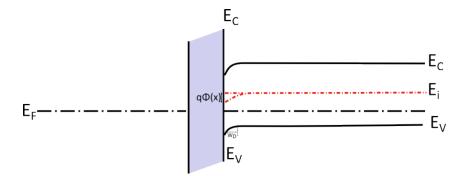

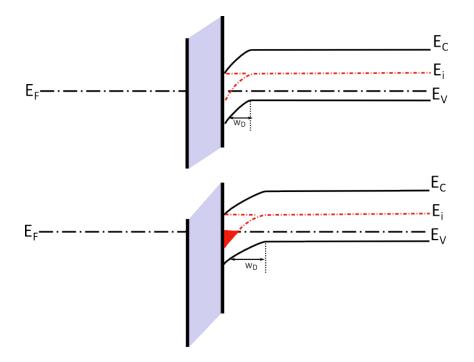

Below are shown the band diagrams of an nMOS capacitor in the flatband condition (Figure 2.2) and under different bias conditions: accumulation (Figure 2.3), depletion (Figure 2.4), inversion and strong inversion (Figure 2.5).

In an ideal MOS capacitor no band bending is observed when the bulk semiconductor and the dielectric are put in contact (see Figure 2.2), that is, there is no charge either in the oxide or at the oxide-semiconductor interface.

Figure 2.2: Energy band diagram for a nMOS capacitor in flatband. In real devices this condition is achieved by applying a voltage to the gate.  $\Phi_M$  and  $\Phi_S$  are the metal and semiconductor work function respectively.

However, when the two interfaces are put together in real MOS capacitors band bending does occur, due to the difference in the work functions of the materials. The band bending changes by applying a voltage to the gate, so, in order to align the Fermi levels it is possible to apply a voltage that counterbalances the difference in work functions, called the flat band voltage,  $\mathbf{V}_{FB}$ :

$$V_{FB} = \Phi_g - \Phi_s \tag{2.1}$$

where  $\psi_g$  and  $\psi_s$  are the gate work function and the semiconductor work function, respectively. These work functions are defined as the difference between the vacuum level and the Fermi level. For simplicity, the contributions of interface charge traps and any charge within the oxide are ignored in calculating the band bending.

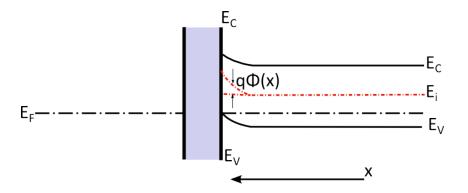

For an n-type (p-type) semiconductor applying a positive (negative) voltage to the gate causes the conduction (valence) band to bend towards the Fermi level causing electrons (holes) to move and accumulate at the surface: the capacitor is said to be in 'accumulation' (Figure 2.3).

If a negative (positive) voltage is now applied to the gate, the valence (conduction) band bends towards the Fermi level causing the electrons (holes) to be repelled from the surface: the device is said to be in 'depletion' (see Figure 2.4). By continuing to decrease (increase) the voltage to the gate, the bands will bend even further causing the Fermi level to be closer to the

Figure 2.3: Sketch of energy band diagram for a nMOS capacitor in accumulation condition.

Figure 2.4: Sketch of energy band diagram for a nMOS capacitor in depletion conduction.

conduction (valence) band and eventually reach the onset of inversion, when the majority carrier concentration will be equal to the donor concentration. Continuing to apply voltage to the gate causes the device to change from n-type (p-type) to p-type (n-type) (see Figure 2.5) i.e. to become 'inverted'.

In inversion is possible to relate the voltage applied to the gate with the flatband voltage, the oxide voltage ( $V_{ox}$ ) and the potential at the surface of the semiconductor ( $\psi_s$ ):

$$V_G = V_{FB} + V_{ox} + \psi_s = V_{FB} + \frac{Q_s}{C_{ox}} + \psi_s$$

(2.2)

where  $C_{ox}$  is the oxide capacitance, and  $Q_s$  is the total charge at the semiconductoroxide. The total charge is composed of the inversion and depletion charge,  $Q_{inv}$ and  $Q_{dep}$ , respectively. The surface potential  $\psi_s$  is defined as the difference between the Fermi level at the surface and the Fermi level in the bulk. The band perturbation potential  $\psi$  is a function of the distance perpendicular to the interface, that is,  $\psi_s \equiv \psi_s(z)$ , and is parabolic. The minimum of this potential is at  $z = W_d$  and at this point  $\psi(= W_d) = 0$ , where  $W_d$  is the depletion layer width. At the surface, z = 0, the band perturbation potential is equal

Figure 2.5: Energy band diagram for a nMOS capacitor in inversion and strong inversion.

to the surface potential, that is,  $\psi(z=0) = \psi_s$ . Solving the Poisson equation and taking the depletion regime gives a depletion layer width:

$$W_{dep} = \sqrt{\frac{2\epsilon_{sc}\epsilon_0\psi_s}{qN_a}} \tag{2.3}$$

where  $\epsilon_{sc}$  is the semiconductor relative permittivity,  $\epsilon_0$  the permittivity of free space, q the electron charge,  $\psi_s$  the surface potential and  $N_a$  the density of ionised acceptors. The depletion charge sheet density is given by

$$Q_{dep} = qNW_{dep} = \sqrt{2\epsilon_0\epsilon_{sc}qN\psi_s} \tag{2.4}$$

for which the surface potential at the onset of strong inversion is two times

the bulk potential

$$\psi_s = 2\psi_b = 2\frac{k_B T}{q} ln\left(\frac{N}{n_i}\right) \tag{2.5}$$

with the bulk potential also given by

$$\psi_b = \frac{E_F - E_i}{q} \tag{2.6}$$

where  $n_i$  is the intrinsic carrier concentration,  $k_B$  is the Boltzmann constant and T the temperature.

In strong inversion the bands are no longer affected by the voltage applied at the gate; the depletion layer width is at its maximum and is given by

$$W_{dep} = \sqrt{\frac{4\epsilon_{sc}\epsilon_0 k_B T ln(N/n_i)}{q^2 N}}$$

(2.7)

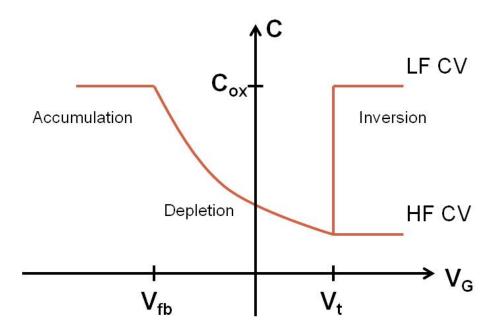

#### 2.1.1 MOS CV characteristics.

Figure 2.6 shows a schematic current-voltage (CV) characteristic for a MOS capacitor, with measurements made at both low and high frequency. The curve can be divided in the 3 regions: in accumulation the capacitor behaves as a regular parallel plate capacitor, so the capacitance measured is the oxide capacitance; as the capacitor enters the depletion region the carriers are repelled away from interface, so the oxide capacitance is in series with the depletion region capacitance; when the capacitor enters inversion the carriers from the bulk cannot respond to a high frequency AC signal, so the curve remains constant at the bottom of the depletion region. However, at sufficiently low frequencies the carriers can respond to the AC signal and the capacitance becomes equal to the oxide capacitance again.

Figure 2.6: CV characteristics for a MOS capacitor for both high frequency and low frequency.

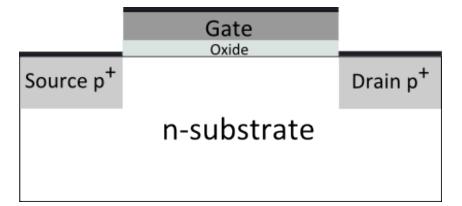

# 2.2 Metal-Oxide-Semiconductor Field-Effect-Transistor (MOSFET).

The metal-oxide-semiconductor-field-effect transistor consist of a MOS capacitor with highly doped contacts, source and drain on either side of the channel, each with a metal contact. A p-channel MOSFET consist of an n-doped body with highly p-doped source and drain, see Figure 2.7. In an n-MOSFET, the doping is of the opposite polarity. The gate oxide is a thin dielectric insulating layer that enables a vertical electric field to be established between the gate metal electrode and the body, but not a leakage current between them. This electric field attracts charge carriers into the channel region and in varying it the conductivity of the channel can be controlled. The basic parameters of the MOSFET are channel length L (the distance between

the drain and the source), channel width W, gate-oxide thickness d, junction depth  $r_j$  and substrate doping N [2, 50].

When no voltage is applied to the gate, the drain and source are

Figure 2.7: Schematic of a pMOSFET. A MOSFET is a four-terminal device: source, drain, gate and substrate. For a pMOSFET the source and drain are  $p^+$  doped and the substrate is n doped.

isolated so no current flows across the channel, the device is in the off-state. The MOSFET behaves as two back-to-back diodes in series between drain and source, that is, a pn junctions. When a negative voltage is applied to the gate, the majority carriers will be repelled from the region under the gate downwards into the substrate, reducing the electron density leading to the formation of a positive charge, the depletion charge. The applied voltage attracts the minority carriers, holes, from the metal contacts to the area under the gate, the channel region, forming an inversion layer that connects the drain and the source and current can now flow between the two (the MOSFET is in the on-state). If a negative voltage continues to be applied there will be a point where the substrate is depleted of electrons near the surface and the conductivity of the semiconductor is inverted [2, 13, 14, 51].

MOSFET operation can be described using the charge sheet approxi-

mation [13, 14, 51, 52], which assumes that the inversion charge is located in a sheet at the semiconductor surface, with no potential drop or band bending occurring across the inversion layer.

The inversion charge,  $Q_{inv}$ , as function of the position along the channel is written as

$$Q_{inv}(x) = -C_{ox} \left( V_G - V_t - V_c(x) \right)$$

(2.8)

where  $C_{ox}$  is the oxide capacitance,  $V_c(\mathbf{x})$  is the potential at the surface in the channel region,  $V_t$  is the threshold voltage, which is defined as the voltage need to start inversion:

$$V_t = V_{FB} + 2\Phi_B + \frac{\sqrt{2\epsilon_s q N_D (2\Phi_B)}}{C_{ox}}$$

(2.9)

The first term refers to the flatband voltage, which ideally should be zero, the second term is the condition for the onset of the inversion layer, and the last term is the necessary voltage at the oxide to form the depletion layer.

The inversion layer is populated by holes that are moving at a velocity, v(x), along the channel. The velocity, denominated carrier velocity, is related to the longitudinal electric field,  $E_l$ , by the carrier mobility,  $\mu$ , which is considered constant and independent of the electric field through the channel:

$$v(x) = -\mu \frac{dV_c(x)}{dx}$$

(2.10)

The drain current,  $I_D$ , is defined via equations 2.8 and 2.10 by

$$I_D = WQ_{inv}(x) \cdot v(x) = C_{ox}\mu W \left(V_G - V_t - V_c(x)\right) \frac{dV_c(x)}{dx}$$

(2.11)

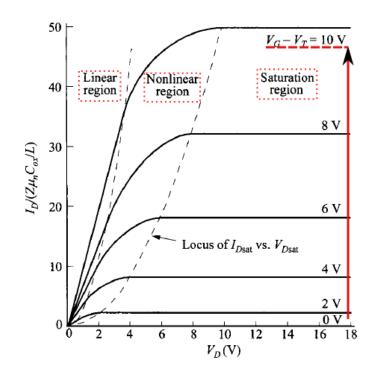

Figure 2.8: Ideal output characteristics of a MOSFET. Both operation regions are represented: saturation region  $(V_D \ll V_G - V_t)$  and linear region  $(V_D \geq V_G - V_t)$ . Reproduced from [53]

Performing the integration from  $V_c(0) = 0$  to  $V_c(L_c) = V_D$ , the expression for the drain current will be:

$$I_D = \frac{\mu C_{ox} W}{L_c} \left[ (V_G - V_t) V_D - \frac{V_D^2}{2} \right]$$

(2.12)

which describes the output characteristics of a MOSFET.

Figure 2.8 shows the drain current plotted as a function of the sourcedrain voltage at different gate voltages. The curves can be divided into two regions, the linear region and the saturation region. The linear region is characterized by a linear increase of drain current with gate voltage and in this region equation 2.12 can be written as

$$I_{D_{linear}} \approx \mu \frac{W}{L} C_{ox} \left( \left( V_G - V_t \right) V_D \right)$$

(2.13)

Increasing the drain voltage leads to a decrease in the inversion charge, reaching a stage with no inversion charge which is the 'pinch-off' point. An increase in the drain current moves the physical position of the pinch-off point in the channel towards the source. In this situation, the drain current depends on the channel length, not on the source-drain voltage, and the device reaches the saturation region. The drain current is then given by

$$I_{D_{sat}} = \mu \frac{W}{L} C_{ox} \left( V_G - V_t^2 \right)$$

(2.14)

## 2.3 Carrier Mobility and Scattering

The carrier mobility is an important parameter in device performance [14, 15], since a higher mobility translates into a higher drive current. The mobility is determined by a range of processes that scatter the charge carriers in the channel and is limited by the scattering mechanism with the highest relaxation rate.

The mobility is related to the transport scattering time  $\tau$  by

$$\mu = \frac{e\tau}{m^*} \tag{2.15}$$

In the presence of multiple scattering mechanisms the mobility can be calculated by summing the inverse relaxation times for each mechanism to find an average relaxation time. For each process, the relaxation rate (inverse relaxation time) is given by solving the Boltzmann equation.

#### 2.3.1 Scattering mechanisms

As the carrier moves along the channel it might encounter impurities, such as defects, which are responsible for the delay in their motion. If the carrier goes from the source and the drain without any impediment it is said to be in the ballistic regime, but this is very rare. Usually the carriers will interact with impurities in the lattice. The main mechanism responsible for scattering are ionized impurities or Coulomb scattering; phonon scattering; surface roughness scattering and alloy scattering.

#### 2.3.1.1 Ionized impurities or Coulomb scattering

There will be a certain level of background impurities in any material, dopants are introduced into the body of a MOSFET to set the electrostatics, and in addition dopants can diffuse into the channel as a result of the heavy doping of the source and drain regions. The amount of dopants in the channel can also increase as a result of diffusion during high temperature stages of device fabrication. What is important for carrier scattering is how many of these impurities are ionised and thereby create an electrostatic potential. Coulomb scattering can also arise from defects at the gate/semiconductor interface that attract charge. The impurities will change the lattice periodicity locally and consequently will change the potential. Since the Coulomb potential is a static potential it is possible for high energy carries to screen this

effect. At low temperatures, when carriers have low energy, and for short channel devices this scattering mechanism is more accentuated and will often be the limiting factor on the carrier mobility [14].

The matrix element  $M_q$  for Coulomb scattering is given by

$$|M_{q}| = \left[\frac{2\pi e^{2}}{\kappa_{0}q}\right]^{2} \int N_{l}(z) \left[F_{l}(q,z)\right]^{2} dz \qquad (2.16)$$

where  $N_l(z)$  is the impurity concentration.

#### 2.3.1.2 Phonon scattering

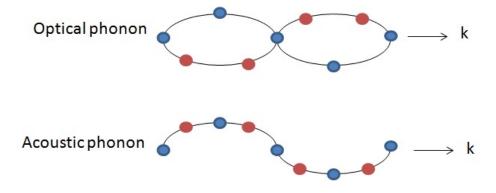

Lattice vibrations (phonons) cause atoms to displace from their equilibrium positions, causing changes in the band structure and hence in the band energies. Thus lattice vibrations act as a perturbation on the potential. There are two branches of phonons: acoustic and optical phonons, see Figure 2.9.

Figure 2.9: Schematic showing the difference between the acoustic and optical phonons with the same wavelength. Taken from [54].

Both Si and Ge have three acoustic phonon modes (one longitudinal and two transverse) and three optical phonon modes (one longitudinal and two transverse). In the longitudinal mode all atoms move in the direction of the wave vector, while in the transverse mode atoms move in the perpendicular direction [2, 55]. Acoustic phonons behave like sound waves with atoms moving together in the same direction. The motion of adjacent atoms in optical mode is in opposite directions.

Scattering by acoustic phonons can be considered to be quasi-elastic, as the phonon energy is small compared to the energy of the carrier. By contrast, optical phonons have a minimum energy that is not small, making optical phonon scattering an inelastic process that modifies the carrier energy.

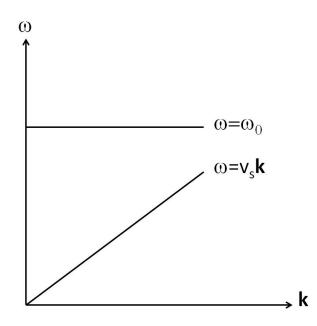

Lattice vibrations behave as the vibrations of the harmonic oscillator, with phonons having an associated energy  $E(\mathbf{k})$  and a momentum  $\mathbf{k}$ . Figure 2.10 shows a schematic version of the phonon dispersion relation for the optical mode  $\omega(\mathbf{k}) = \omega_0$  and acoustic mode  $\omega = v_s \mathbf{k}$ .

Figure 2.10: Schematic representation of phonon acoustic and optical modes.

temperature, since the scattering rate will increase with temperature as the number of phonons increases.

#### 2.3.1.3 Surface roughness scattering

Since the interface between semiconductor and dielectric is never perfectly smooth, surface roughness causes carriers to scatter. The interface roughness scattering process is parameterised by an average height  $\Delta$  and a correlation length  $\Lambda$  [13, 14, 56]. It assumes a Gaussian distribution which is valid when  $\Delta \ll L$  and  $\Lambda \gg L$ .

#### 2.3.1.4 Alloy scattering

An alloy implies the introduction of a different atom, for example Si and Ge, which causes atomic disorder due to the change in the local band structure. When the concentration of Ge is of 50% the alloy scattering has its maximum [14, 56, 57]. However, in most cases for devices made of SiGe, alloy scattering is not a dominant scattering mechanism because interface roughness and impurity scattering are far more important processes in real materials [58].

## 2.4 Magneto Transport theory

#### 2.4.1 The Hall effect

An electric field  $E_x$  is applied in the x direction and a current density  $I_x$  flows through a cross section of a metal bar, A. A magnetic field  $B_z$  perpendicular to the surface is also applied. As a result, the Lorentz force will deviate the electrons in the negative direction of y. Electrons will accumulate at one end of the bar creating an electric field in the y direction,  $E_y$  (the Hall field). This implies that the two forces are in balance and current will flow in the x direction.

The sheet resistivity of the bar is given by

$$\rho_{xx} = \frac{V_x}{I_x} \frac{w}{l} \tag{2.17}$$

and has units of  $\Omega/sq$ . The velocity of the carries is related to the current I by  $I = n_s qvw$ , where  $n_s (= nt)$  is the sheet carrier density. The Hall voltage, that is, the voltage across the bar produced by the electric field, is given by [59]

$$V_H = \frac{IB}{n_s q w} \tag{2.18}$$

where  $n_s$  is the sheet carrier density, q the electron charge and w the width of the bar. The Hall resistivity is given by

$$\rho_{xy} = \frac{V_H}{I} = \frac{B}{n_s q} = R_H B \tag{2.19}$$

From Equations 2.17 and 2.19 we deduce

$$n_s = \frac{IB}{qV_H} \tag{2.20}$$

The conductivity  $\sigma$  is defined by  $nq\mu$  and at low magnetic fields, that is,  $\mu B << 1$  [53, 59]:

$$\rho_{xx} = \frac{1}{n_s q \mu} \tag{2.21}$$

$$\mu_{H} = \frac{1}{n_{s}q\rho_{xx}} = \frac{\rho_{xy}}{B\rho_{xx}} = \frac{1}{B}\frac{V_{H}}{V_{x}}\frac{i}{w}$$

(2.22)

for high fields, that is  $\mu B >> 1$ , the conductivity is defined by

$$\rho(B) = \rho_{xx} = \frac{\sigma_{xx}}{\sigma_{xx}^2 + \sigma_{xy}^2} \tag{2.23}$$

$$R_{H}(B) = -\frac{\rho_{xy}}{B} = -\frac{1}{B}\frac{\sigma_{xy}}{\sigma_{xx}^{2} + \sigma_{xy}^{2}}$$

(2.24)

where  $\sigma$  is the conductivity.

In the previous calculations we have assume a single carrier is present. For multiple carriers we have

$$R_H = \frac{\pm n_1 \mu_1^2 \pm n_2 \mu_2^2}{q \left( n_1 \mu_1 + n_2 \mu_2 \right)^2}$$

(2.25)

for low fields approximation. Which becomes

$$R_H = \frac{1}{q(\pm n_1 + \pm n_2)} \tag{2.26}$$

in high fields. In this approximation, carriers will complete many orbits around the magnetic flux lines before being scattered. This orbits have an angular frequency  $\omega_c = qB/m^*$ . This angular frequency is called the cyclotron frequency. This frequency leads to the formation of Landau levels which are given by

$$E_n = \hbar\omega_c \left(n + \frac{1}{2}\right) \tag{2.27}$$

with n = 0, 1, 2, ...

With increasing magnetic field, the separation between two adjacent Landau levels will increase. The density of states associated with each level is given by [60],

$$n_{2D} = \frac{eB}{h} \tag{2.28}$$

The number of levels occupied is given by the filling factor,  $\nu$ :

$$\nu = \frac{hp_s}{eB_0} \tag{2.29}$$

where  $p_s$  is the sheet carrier density and  $B_0$  is the fundamental field. For  $\nu$  integer the Fermi level is located in between two Landau levels so no scattering occurs.

#### 2.4.2 Shubnikov-de-Haas effect